CRC模块

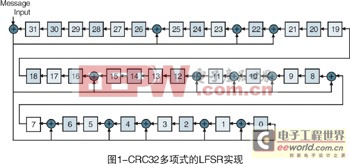

CRC 的硬件实现使用一个简单的 LFSR。这种电路虽然实现起来简单,但对于一个n位数据流来说,要占用n个时钟周期来计算CRC值。在必须以较高速度处理数据帧的高速数据网络应用中,这样的延迟是无法忍受的。这类高速网络应用迫切需要对并行数据流实现CRC生成和校验。

Virtex-5 LXT/SXT器件中实现的CRC模块可帮助设计人员加速校验和计算。

Virtex-5 LXT/SXT器件中的 CRC硬模块基于CRC32多项式。Virtex-5 FPGA含有CRC32和 CRC64 两种硬模块,能以一个时钟周期的延迟为4位和8位数据输出生成CRC。其界面简单易用。硬模块对给定的消息流起着CRC计算器的作用,同时提供一些针对 CRC的参数作为输入。CRC的比较功能已经超出硬模块的范围,应集成到FPGA架构中。

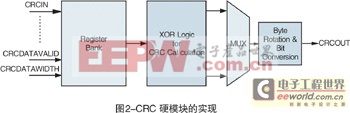

FPGA 中的每个CRC硬模块异步计算一个32位校验和。

图2是说明硬模块架构的模块级图。CRC硬模块提供一个位反演和字节反转的输出。

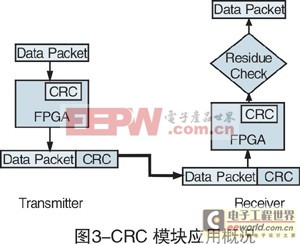

图3所示为CRC硬模块的应用概况。在发射器上,CRC经计算后附加到给定数据包的尾部。在接收器上,对连带发射器所附加的CRC一起接收到的整个数据包重新计算CRC。