4)可选的管理接口

管理接口是一个独立的可选端口,其地址、数据和控制信号相对于其他模块是独立的,提供了和CoreConnec总线的交互能力,可挂在MicroBlaze软核或PowerPC硬核处理器,可用于配置GEMAC核以及通过MDIO接口直接读写外部PHY芯片的内部配置寄存器。该模块包括用户管理的接口和MDIO接口两部分,后者直接与PHY芯片相连,全部接口信号的简要说明如10-13所列。

表10-13 管理模块的接口信号

5)复位操作

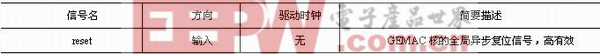

管理模块具备自己独立的软件复位信号,但当管理接口模块被旁路掉,其相应的配置信号被作为configuration_vector[64:0]输入信号使用。此外,GEMAC核提供了硬件复位信号,如表10-14所列。

表10-14 复位信号列表

6)GMII模块

GMII模块的接收信号一般都是直接连到PHY芯片上,负责和PHY芯片的数据交互,其信号和PHY芯片的接口是一一对应的,如表10-15所列。

表10-15 GMII模块接口信号列表

配置完成后,可在工程管理区选中GEMAC核,在过程管理区,点击“View HDL Instantiation Template”命令,查看其例化代码,它在代码中的例化方法和一般IP Core的方法是一样的。

10.5 本章小结

高速串行传输技术是FPGA未来的三大应用领域之一,本章主要介绍了Xilinx公司的Rocket I/O解决方案。首先给出高速传输的背景,指出串行方式是吉比特以及更高速率链路的必然选择。其次,给出了吉比特串行传输的通用架构,为后文做好铺垫。接着重点介绍了Xilinx公司Rocket I/O的系统组成、相关协议、时钟设计方案、开发要素以及Rocket I/O的使用方法。最后说明了千兆以太网MAC控制器IP Core的使用方法。读者需要注意的是Rocket I/O是Xilinx高端FPGA中的内嵌组件,和DCM、硬核乘法器、块RAM等的使用方法是一样的,可通过IP Core调用。高速传输是一种新技术,开发难度较大,本章只是介绍了其中的主要核心部分和基本原理,还需要读者阅读大量的文献和实际操作才能熟练开发相关系统。