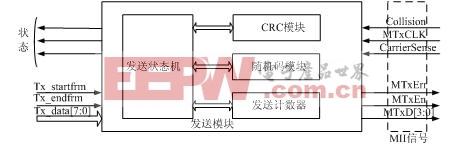

图10-31 以太网MAC发送模块的结构示意图

发送状态机由Idle_State、Preamble_State、Data0_State、Data1_State、PAD_State、FCS_State、IPG_State、Jam_State、BackOff_State、Defer_State 等十个状态组成。其状态转移图如图10-32所示。

图10-32 发送状态机的状态转移图

系统复位后,发送模块即进入Defer_State状态,并一直检测载波侦听(CarrierSense)信号。当载波侦听信号变成无效(表示信道空闲)时,状态机进入IPG_State状态。此后,在等待一个帧间间隙之后,状态机进入Idle_State状态。如果在帧间间隙的前2/3个周期检测到信道忙信号,状态机将重新回到Defer_State状态。

状态机进入Idle_State状态之后,发送模块将检测载波侦听信号和主机接口的发送请求。若主机模块请求发送,状态机将进入Preamble_State状态,发送模块即通知PHY发送开始,同时开始发送前序码(7个0x5), 然后发送帧起始定界符(SFD, 0xd)。状态机进入Data0_State后,发送模块将发送一个数据字节的低4位(LSB nibble),当其进入Data1_State状态后,发送模块则发送数据字节的高4位(MSB nibble)。随后,状态机一直在data0和data1之间循环,直到数据发送完毕。当还剩一个字节时,主机模块将通过发送帧结束信号来通知发送模块。如果数据帧的长度大于最小帧并且小于最大帧,状态机就进入FCS_State状态,此时发送模块则将CRC生成模块生成的CRC值添加到帧的FCS字段中并发送给PHY。

帧发送完之后,状态机进入Defer_State 状态,之后是IPG_State和Idle_State状态。此后状态机又回到初始状态,以重新等待新的发送请求。如果数据帧的长度小于最短帧,状态机就进入PAD_State状态,发送模块根据系统设置确定是否在数据之后添加填充码。然后,状态机进入FCS_State状态。如果数据帧的长度大于最大帧,而系统设置又支持发送超长帧,那么,状态机就进入FCS_State状态;如果不支持发送超长帧,发送模块将放弃发送,状态机直接进入Defer状态,然后是IPG状态,最后回到Idle状态。

在发送数据的过程中,发送模块会一直检查冲突检测信号(collision detected)。如果发现冲突且状态机正处于Preamble_State,状态机将在发送完前序码和SFD之后进入Jam_State,并发送拥塞码,然后进入BackOff状态,以等待重试。之后,状态机经过Defer和IPG回到Idle状态。如果此时重试次数计数器的值没有达到额定值,发送模块将重新开始发送刚才的帧,并将重试次数计数器的值加1;如果发现冲突且状态机处于data0、data1或FCS状态,而且没有超过冲突时间窗,那么状态机将马上进入Jam状态发送拥塞码,之后经过BackOff、Defer、IPG、回到Idle,并根据重试计数器的值决定是否重新发送刚才的数据帧;如果检测到发生冲突的时间超过了冲突时间窗,状态机将进入Defer状态,然后经过IPG到IDLE状态,并放弃重试。

在全双工模式中发送帧时,不会进行延迟(defer), 发送的过程中也不会产生冲突。此时,发送模块将忽略PHY的载波侦听和冲突检测信号。当然,帧与帧之间仍然需遵守帧间间隙的规则。因此,全双工模式下的发送状态机没有Jam_State、BackOff_State、Defer_State三个状态。

2)MAC接收模块

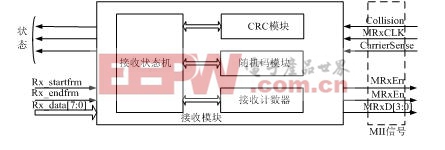

MAC接收模块结构如图10-33所示,负责数据帧的接收。当外部PHY将通信信道的串行数据转换为半字节长的并行数据并发送给接收模块后,接收模块会将这些半字节数据转换为字节数据,然后经过地址识别、CRC校验、长度判断等操作后,再通过主机接口写入外部存储器,并在主机接口模块的接收队列中记录帧的相关信息。此外,接收模块还负责前序码和CRC的移除。

图10-33 以太网MAC接收模块的结构示意图