千兆以太网MACIP Core的配置界面如图10-36所示。GEMAC控制器所实现的主要功能如图10-37所示,包括发送引擎、接收引擎、流控制、GMII接口、客户发送接口、客户接收接口以及客户管理接口。

图10-37 千兆以太网MACIP Core的主要功能示意图

下面给出相应模块的功能和接口信号说明。

1)发送引擎

发送引擎通过客户发送端口接收以太网的数据帧,并在帧头添加帧引导区域,甚至在帧长小于最短要求时,添加一定的冗余比特。同时,该模块还会在连续的数据帧之间插入以太网协议所规定的最小延时,将用户数据转化成标准的GMII数据帧,并送至GMII模块。在应用时,面向用户的操作就是将用户数据读入GEMAC核内部

该模块接口信号的简要信息如表10-10所列。

表10-10 发送引擎接口信号列表

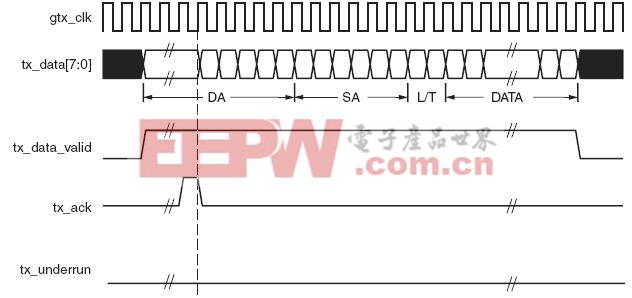

发送引擎的时序如图10-38所示。当客户端有数据发送时,将tx_data_valid拉高,同时将数据的第一个字节置于tx_data端口;当GEMAC将第一字节数据读入后,会将tx_ack信号拉高,用户端逻辑检测到tx_ack为高时,要在下一个时钟上升沿将其余的数据发送到数据端口上,当数据发送完毕后,将x_data_valid拉低。

图10-38 发送引擎的时序图

2)接收引擎

接收引擎接收来自GMII模块的数据,去掉帧头的引导区域,包括为了增加帧长的冗余比特。此外,该模块还能根据数据帧中的检验序列区域、接收到的GMII错误码字以及帧长信息完成错误检测,主要接口信号的简要说明如表10-11所列。

表10-11 接收引擎接口信号列表

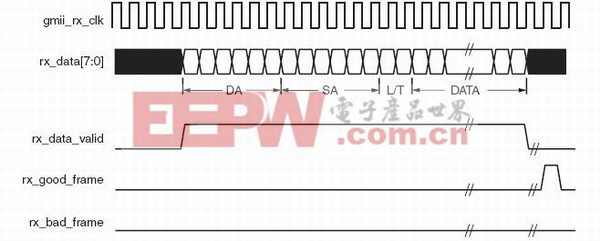

接收引擎的时序如图10-39所示。客户端逻辑必须在任何时候都准备好接收数据,因为在GEMAC核中没有接收缓存,有时延就会丢失数据,因此用户可自己添加缓冲逻辑。rx_data_valid为高时立即开始接收连续数据,在检测到rx_data_valid变低后,判断rx_good_frame信号的电平,如果为高则继续处理该帧数据,否则直接丢弃。

图10-39 接收引擎的时序图

3)流控制

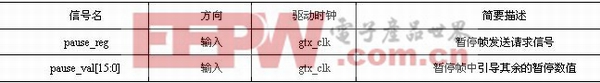

流控制模块是根据IEEE 802.3-2002标准的31项条款设计的,在发送时附带暂停帧,接收时也需要对其处理。在GEMAC核中,它是自动配置的,同时,也提供了用户自定义的配置端口,如表10-12所列。

表10-12 流控制接口信号