ModelSim和Synplify Pro是比较通用的第三方仿真和综合软件。在这里如果我们选择了使用第三方的软件进行综合及仿真的话,在后面执行相应步骤的时候ISE Navigator就会自动寻找并打开相应的软件。

(4)添加设计文件。

填写好FPGA型号和使用的综合,仿真软件后,单击“Next”按钮打开如图2.72所示的创建源文件对话框。

图2.72 创建源文件对话框

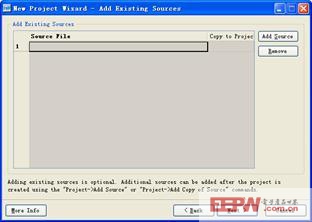

在这个对话框里面,允许用户为即将建立的工程创建一个新的源文件,并且这里只可以创建一个源文件。其他的要在工程建立以后创建,也可以在创建工程以后再建立所有的源文件。直接单击“Next”按钮,进入如图2.73所示的添加源文件对话框。

在这个对话框里面为即将建立的工程添加已经存在的源文件。如果没有现成的源文件,直接单击“Next”按钮,完成新工程的创建。

(5)完成工程创建。

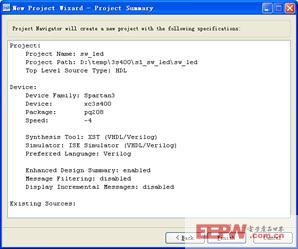

在如图2.74所示的新工程信息对话框中,列出了新建工程的相关参数及属性。

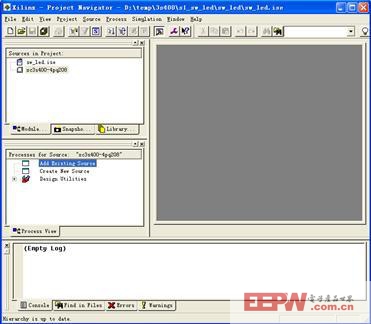

在这个对话框里面显示将要创建的工程的全部信息,确认无误后单击“Finish”按钮,Project Navigator将自动创建一个名为sw_led的工程。如图2.75所示是新工程的界面。

图2.73 添加源文件对话框

图2.74 工程信息对话框

图2.75 工程创建后的界面

创建好工程以后就要为工程添加源文件了,具体方法如下。

为工程添加源文件有两种方式,可以双击“Process View”对话框里面的“Create New Source”,也可以在“Module View”对话框里面的“xc3s400-4pq208”图标上面单击鼠标右键,选择“New Source…”选项,如图2.76所示。

图2.76 添加源文件的两种方式

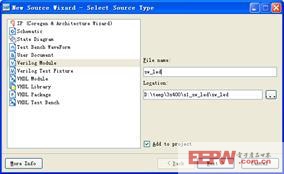

选择“New Source”,弹出如图2.77所示的新建源文件对话框。

图2.77 新建资源对话框

在右面的“File Name”栏里面填写要生成的源文件的名字,在“Location”栏填写源文件保存的路径,一般位于工程文件夹里面,没有特殊需要不必更改。另外一定要选择“Add to project”选项,然后在左边的一排图标里面选择源文件的类型后单击“Next”按钮,进入如图2.78所示的Verilog源定义对话框。

可以在上面的对话框里面输入源文件的模块名称和管脚定义,也可以先不输入,后面写程序的时候自己输入。单击“Next”按钮,完成源文件的创建,在如图2.79所示的对话框中列出了新建源文件的一些信息。

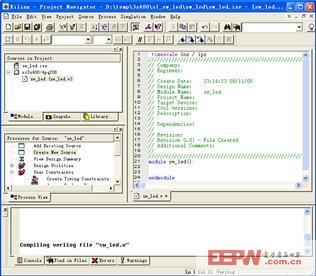

确认信息无误后,单击“Finish”按钮,ISE将生成名为sw_led.v的源文件,如图2.80所示。

图2.78 新建Verilog文件设置对话框

图2.79 新建源文件信息对话框

图2.80 添加新资源后工程界面

用户可以在工作区中开始进行设计的输入,也可参考实例代码中的例程,将代码直接复制到新建的Verilog文件下。输入好程序以后,保存源文件,完成设计的输入。