DSP 版

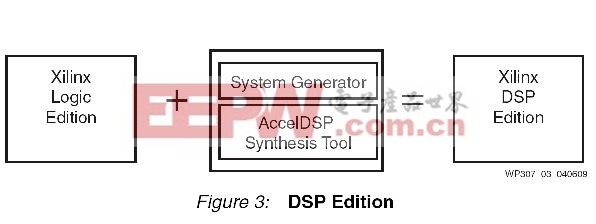

新的 DSP 版包括赛灵思逻辑版以及赛灵思 DSP捆绑包(System Generator 开发环境和AccelDSP 综合工具)。参见图 3。

图 3:DSP 版

DSP 版主要以算法开发人员为目标受众,可帮助他们在赛灵思 FPGA 中实施复杂的算法。由于工作流程高度自动化,因此用户无需熟悉 HDL。

在流程中,算法开发人员首先在 The MathWorks 推出的 MATLAB® 软件环境中创建算法和算法的行为模型,然后再在 MathWorks’ Simulink® 产品中测试行为模型,在 MATLAB 和 Simulink 软件之间迭代调试算法,直到算法行为达到预期为止。随后,用户则能用赛灵思 DSP 版来优化和实施赛灵思 FPGA 算法。

算法开发人员可在 DSP 版中用 System Generator 来取代构成所有、大部分或部分算法的行为模块。这些模块包含了赛灵思 CORE Generator 库中的优化 IP,也就是说用户也能通过定制黑盒子用自己的HDL来取代所有或部分模块。如果用户在MATLAB软件中创建了定制算法但没有算法的 VHDL 表达,那么算法开发人员可用 AccelDSP 综合工具自动将定制算法综合到 VHDL 中,并创建新的 System Generator 模块。该模块可用 System Generator设计中的其他模块来替代。System Generator 中的所有算法模块被填充后,用户按下按钮,System Generator 就能自动运行 ISE 软件的放置和布线工具,让工具自己去实施 FPGA 算法表达。这样,算法开发人员只需几分钟就能在赛灵思 FPGA中实施算法,并了解算法在真实硬件上的工作情况。

DSP 版可链接至 Simulink 软件,这使算法开发人员能够在 Simulink 和 MATLAB 环境中重复使用已开发的测试基准来测试其算法,从而确保硬件算法和软件算法的版本行为一致。此外,算法开发人员还能结合使用 DSP 版及 Simulink 和 MATLAB 软件来执行协同仿真任务,同时还能对算法进行故障排除和修改,以实现最佳的性能与功能。例如,如果算法开发人员在开发过程中发现众多行为模块之一需要调整,则可在 FPGA 中运行已知状态良好的模块,以便通过对故障模块的反复调节测试迭代来加速验证工作。硬件协同仿真的运行速度比纯软件仿真加快了 1,000 倍;而且算法越复杂,硬件仿真相对于软件仿真的加速就越明显。

在 ISE 设计套件 11.1 软件中,System Generator 工具可运行在 Linux 与 Microsoft Windows 上。