您以往可能听说过C语言级硬件综合。不管您听说过什么,C语言级算法综合已成为系统级设计的捷径。当前有超过400名用户正在成功利用Vivado高层次综合(HLS)技术开发符合C、C++和SystemC语言规范的赛灵思All Programmable器件用IP硬核。

Vivado HLS通过下列功能,让系统和设计架构师走上IP硬核开发的捷径:

♦ 算法描述、数据类型规格(整数、定点或浮点)和接口(FIFO、AXI4、AXI4-Lite、AXI4-Stream)抽象化;

♦ 采用可提供最佳QoR(结果质量)的基于指令的架构感知型编译器;

♦ 使用C/C++测试平台仿真、自动化VHDL/Verilog仿真和测试台生成功能加快模块级验证;

♦ 发挥整套Vivado设计套件的功能,将生成的IP硬核轻松嵌入基于RTL的设计流程中;发挥Vivado System Generator for DSP的功能,将生成的IP硬核轻松嵌入基于模型的设计;发挥Vivado IP集成器(Vivado IP Integrator)的功能,将生成的IP硬核轻松集成到基于模块的设计。

这样硬件设计人员就有更多时间投入到设计领域的探索中,即有更多时间评估备选架构,找出真正理想的设计解决方案,轻松应对各种严峻的系统设计挑战。例如设计人员将行业标准的浮点math.h运算与Vivado HLS结合使用,就能够在实现较手动编码的RTL更优异的QoR的同时,让线性代数算法的执行速度呈数量级提高(10倍),如表1所示。

表1:Vivado HLS实现的QoR

|

雷达设计 (1024x64浮点QRD) |

RTL方法 (VHDL) |

Vivado HLS |

|

设计时间(周) |

12 |

1 |

|

时延(毫秒) |

37 |

21 |

|

资源 • BRAMS • FF • LUT |

273 29,686 28,512 |

1 38 14,263 24,257 |

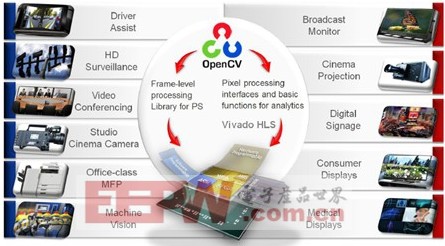

通过集成到OpenCV®环境中的预先编写、预先验证的视觉与视频功能,Vivado HLS还能加速基于赛灵思Zynq®-7000 All Programmable SoC器件的系统的实时Smarter Vision算法的开发工作。此类系统使用运行在Zynq SoC的双核ARM®处理系统上的软件和位于Zynq SoC高性能FPGA架构上的硬件来运行这些算法(如图6所示)。

|

驱动程序辅助 |

|

|

广播监控器 |

|

高清监视 |

OpenCV |

放映 |

|

|

视频会议 |

处理系统(PS)帧级处理库 |

像素处理接口和基本分析功能 |

|

|

电影摄像机 |

|

|

数字标牌 |

|

办公用多功能打印机 |

|

|

消费类显示器 |

|

机器视觉 |

|

|

医疗显示器 |

使用Vivado HLS Smarter Vision库的各项功能,用户借助硬件加速就能迅速实现复杂像素处理接口和基本视频分析功能的实时运行。

(如欲立即开始使用Vivado HLS,敬请下载《如何使用Vivado高层次综合的FPGA设计》。这是一本以赛灵思对其主要客户举办的培训为依据的综合性用户指南。该指南可快速向软件工程师教授如何将软件算法从处理器上移植到赛灵思All Programmable FPGA和SoC的可编程逻辑上,加快他们的代码运行速度。)

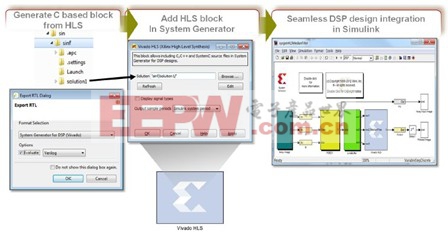

理由五:利用System Generator for DSP实现基于模块的DSP设计集成

如上文所述,Vivado设计套件系统版本提供System Generator for DSP,这是一款行业领先的将DSP算法转换为高性能生产质量级硬件的高级设计工具,转换所需时间仅为传统RTL设计方法的几分之一。Vivado System Generator for DSP可让开发人员运用业界最先进的All Programmable系统建模工具(MathWorks®提供的Simulink™和MATLAB™),无缝集成那些可用Vivado HLS综合到硬件中的算术函数、SmartCORE™与LogiCORE™ IP、定制RTL以及基于C语言的模块,从而加速高度并行系统的开发。图7所示的是使用Vivado HLS和Vivado System Generator for DSP将基于C语言的模块集成到Simulink中的设计流程。

Vivado System Generator for DSP提供自动定点/浮点硬件生成功能、可将Simulink仿真速度提高1000倍的硬件协同仿真功能、用于基于RTL的Vivdo设计流程的系统集成功能,以及用Vivado IP集成器实现的基于模块的设计功能,可进一步加快系统实现。

理由六:利用Vivado IP集成器实现基于模块的IP集成

Vivado设计套件提供行业首款即插即用IP集成设计环境Vivado IP集成器 (Vivado IPI),打破了RTL设计生产力的局限性。

Vivado IP集成器提供图形化、脚本编写(Tcl)、生成即保证正确(correct-by-construction)的设计开发流程。此外,它还提供具有器件和平台意识的环境,以及强大的集成调试功能,能支持主要IP接口的智能自动连接、一键式IP子系统生成、实时设计规则检查(DRC)和接口修改传递等。

设计人员在使用Vivado IP集成器建立IP模块之间的连接时,工作在抽象的“接口”层面而非“信号”层面。抽象上升到接口层面大大提高了设计人员的生产力。虽然主要使用的是业界标准的AXI4接口,IP集成器也支持数十种其他常用接口。

工作在接口层面的设计团队可以快速组装采用Vivado HLS与Vivado System Generator for DSP创建的IP、赛灵思SmarteCORE与LogiCORE IP、联盟成员IP和专有IP的复杂系统。结合使用Vivado IP集成器和Vivado HLS可显著降低开发成本,仅为使用RTL方法的1/15。