将堆叠硅片互联技术投入生产

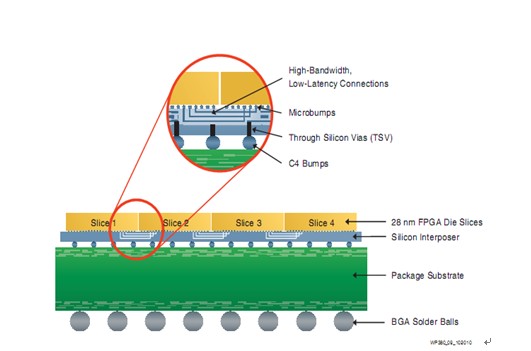

结合使用硅通孔技术与受控的塌落芯片连接 (C4) 焊锡凸块,赛灵思得以将 FPGA/中介层堆叠用倒装片组装技术贴装到高性能封装基片上(如图6 所示)。这种大节距硅通孔为并行和串行 I/O,电源/接地、时钟、配置信号等提供了封装和 FPGA 之间的连接。

图 6:封装基片

由多项正在申请专利的创新堆叠硅片互联技术能够通过超过 10,000 个器件规模的连接提供每秒数 Tb 的芯片间带宽,足以满足最复杂的多芯片设计需求。赛灵思采用该新技术开发的 Virtex®-7 FPGA 系列具有无与伦比的功能,其中包括:200 万个逻辑单元、65 Mb block RAM、2,375 GMACS 的 DSP 性能(4,750 GMACS 用于对称滤波器)、1,200个支持1.6Gb/s LVDS并行接口的 SelectIO 引脚、以及72个能够提供 1,886Gb/S 双向总带宽的串行收发器。

将堆叠硅片互联技术投入生产

赛灵思在采用堆叠硅片互联技术开发 FPGA 的开发策略是从广泛建模以及一系列用于设计实现、可制造性验证和可靠性评估的测试器件(或测试平台)的创建开始的。

应力仿真模型还显示出堆叠硅片技术的另一项优势。与单片解决方案相比,硅中介层起到了缓冲作用,降低了低介电电介质应力,并提升了 C4 凸块的可靠性。

对堆叠芯片进行的广泛的热效应仿真显示,采用堆叠硅片互联技术的器件的热性能可与单片器件相媲美。

经过与业界领先的供应商五年多的共同研发,以及在一系列多种测试平台上的广泛测试,赛灵思首批采用堆叠硅片互联技术的 FPGA可以 顺利走向量产。这些测试平台主要用于工艺模块开发与集成、可靠性评估、供应链确认、设计实现、中介层裸晶良品测试 (KGD) 以及微凸块电迁移 (EM) 规则验证等。

迄今为止,通过测试平台成功完成的可靠性测试包括:

赛灵思拥有稳健可靠的技术供应链,为生产业界首批采用堆叠硅片互联技术的 FPGA 做好了充分准备。TSMC、Ibiden、等相关合作伙伴将充分利用他们的资源和技术专长,共同生产 28nm FPGA 和 65nm 硅中介层、互联层、微凸块、C4焊球和封装基片,并进行晶圆减薄、芯片分离、叠层芯片连接和封装组装等工序。