3、赛灵思的解决方案

赛灵思采用的方案能够有效解决采用 28nm 技术的大容量 FPGA 投产的问题,如下图所示:

赛灵思解决方案使用了基于 TSV 的芯片中介层,该中介层采用的技术在图像传感器和功率放大器等大批量应用中得到了充分的验证。此外,其还支持超长的互连结构,不仅可实现较低的延迟,而且还能作为片上连接结构的扩展。这样我们就能采用 N 芯片解决方案,其性能水平可接近 400MHz。多芯片封装类似于单片解决方案封装,这样一旦缺陷密度水平趋于成熟,我们就可转而选用单片解决方案。

可通过微型焊球将 FPGA 芯片连接至芯片中介层,其支持较大的引脚数以及高度的可靠性。由于芯片和中介层的热连接类似,因而热应力非常低。

中介层采用 C4 技术连接至下一层载体。C4 技术最初由 IBM 开发,主要用于其高性能、高可靠性计算机系统。较大的焊球能吸收芯片基板和下一级载体之间的热应力。

多层结构使用的技术非常成熟,并应用于各种大批量产品的批量制造中。但是,将业经验证具有卓越性能的不同技术结合在一起不仅需要创造性,而且这也是一种风险较低的办法来提升 28nm 高容量 FPGA 产品的单位产量。

虽然当前方案是在中介层上集成了 4 颗特性类似且与全面集成型设计的门数量相当的 FPGA 芯片,但堆叠硅片互联技术也可实现将不同特性的 FPGA 芯片组装在一起,这些特性包括 SERDES、高密度 CAM 结构以及处理器引擎等。

此外,还能开发可编程 ASSP 产品,其中可能包含两或三颗 ASSP 芯片和一或两颗 FPGA 芯片。另外还可针对在中介层上集成的构建块功能,混合采用多种不同的工艺技术。

我们或许需要修改 FPGA 架构来支持专用的平台解决方案,不过这种方案与设计全面的 ASSP 或标准单元 ASIC 相比成本低很多。

赛灵思技术在 28nm 技术节点上既具备长期优势也具备短期优势,因为其在 20nm 和未来更先进的工艺节点上都能继续发挥作用。

赛灵思将采用系统性低风险方案来实现多芯片制造,从而降低最终客户的风险。我们能提供高门数的 FPGA 产品,确保实现极富竞争优势的性能和功耗。

堆叠硅片互联技术的各个部分均已实现大批量制造,因而无论是技术风险还是制造性和可靠性风险都非常低。

4. 应用的潜在优势

从应用分析中可见,各种系统都能采用该技术。我们能够获得标准单元 ASIC 和专用标准产品的一部分市场份额,同时还能通过增强系统功能进一步扩展原有的 FPGA 市场。

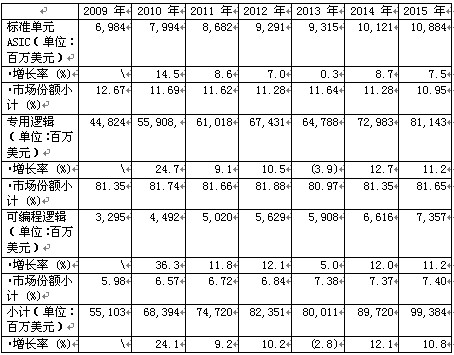

下表显示了硬件定制方案的市场前景。

表 1

标准单元 ASIC、ASSP 和可编程逻辑的市场

IBS 公司,“系统 IC 市场趋势”(2010年第二季度全球系统 IC 产业服务),2010 年 8 月