1. 概要

为尽早推出 28nm 高容量 FPGA 产品,赛灵思 (Xilinx) 通过以下工作满足了关键需求:

充分利用 FPGA 的重复结构创建分区,并将分区按编号组合起来以创建单个产品,相对于采用大型单片产品而言,在工艺节点生命周期的早期即实现了高良率特性。

使用具有高可靠性的微凸块,将硅片连接至硅中介层。

使用 TSV 技术和在大批量生产中获得全面验证的高密度互联技术构成中介层,实现低时延的芯片间通信和倒装片封装。

使用大面积标准焊接凸块,实现从中介层到下一级的高可靠性连接功能。

堆叠硅片互联技术能充分满足大批量生产需求,从而确保 28nm FPGA 产品能够具备卓越的高可靠性和大容量优势。赛灵思将一系列业经验证的大批量生产技术完美结合在一起,为需要大容量FPGA 的系统提供了高度创新的解决方案。

2. 挑战性综述

赛灵思的 Virtex-7 产品包含多达 200 万个可用的逻辑门,与 Virtex-6 系列相比,可将每个门的功耗降低 50%。此外,Virtex-7 系列还支持速率高达 28Gbps 的高速 SERDES,并集成了大量 DSP 模块。

较大容量 FPGA 产品有潜力成为系统设计的核心,而不是仅具备支持随机门的功能,因而可为客户提供众多显著优势,如在各种系统类型和应用细分领域中实现全新的产品系列。

需要解决的一大关键问题领域就是,如何用新的技术节点改进超大尺寸产品的低良率问题。随着缺陷密度水平的降低,良率会随着时间的推移不断上升,但这需要 18 到 24 个月的时间。

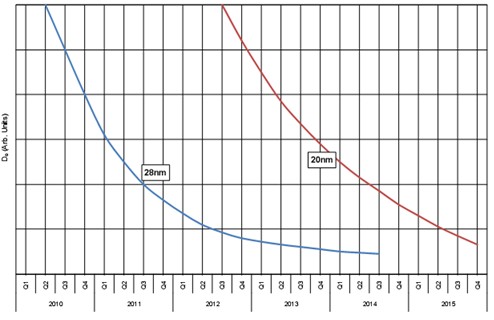

下图显示了 28nm 和 20nm 技术在缺陷密度方面的改进情况。

图 1

28nm 和 20nm技术的缺陷密度水平

新技术缺陷密度水平的降低相对较快,但也要 18 到 24 个月才能实现大尺寸芯片的高良率。赛灵思采用的方案是通过 FPGA 产品的重复结构实现 N 个较小芯片,此外, N 可以是 2、4 或更多,N 个芯片组装在一起就形成了一个有着相同特性的大型芯片。

这就克服了分别封装 N 个芯片所带来的挑战,因而不会出现芯片、封装以及开发板之间来回出现的延迟,有效避免了高功耗和延迟过长的问题。

由于使用了较小尺寸的芯片,我们能够快速提高晶圆产量,避免了与大尺寸芯片相关的良率下降问题。

随着缺陷密度水平的降低,多芯片与单芯片解决方案之间的净良率差异将减小。但是,使用较小芯片的性能优势仍保持不变。

大尺寸芯片上的大容量 FPGA 互连长度非常长,对于采用 28nm 工艺的紧密栅距互连结构而言,物理参数稍有变化就会对关键路径的延迟产生较大影响。随着技术不断成熟,诸如TSMC等晶圆厂商将逐渐缩小延迟差异。

因而,我们面临的关键挑战是,如何使用多芯片方案,在新技术节点刚刚可用的早期阶段实现低延迟互连。