很明显,我们需要对设计进行深层研究。我们的解决方案是采用自主开发的 FireStark 协议,它是一种基于 UDP 的协议,位于 AXI 以太网 DMA 驱动程序内部。通过调整 MicroBlaze Linux 内核驱动程序和把 FPGA 放在专用网络上,我们现在能够在 60 秒内完成对整个 2Gb 数据的下载,速度提高 70 倍。如果使用高达 6Kb 的巨型帧进行测试,速度还可以翻倍,即超过 70Mb/s。关键之处在于,这说明使用 DMA,即便是在较慢的 100MHz 的 MicroBlaze 时钟下,也能够在存储器和网络之间实现极高的数据吞吐能力。

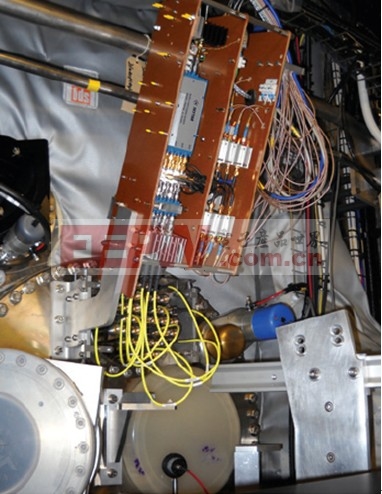

图 3:连接到 MAST 托卡马克装置的 RF 电子设备能够将接收到的 6GHz 至 40GHz 的信号降频为 250MHz 带宽信号,供 FPGA 数据采集盒处理。

FPGA 到 PC 机的时延经测量为 129µs +/- 13µs(真正的时延会更低,因为该测量值包含数据包穿越交换机、通过 PC 内核、到达网络堆栈以及最终进入用户区域的时延)。我们还准备测量 FPGA 之间的时延,预计会更低。

时钟同步

我们的托卡马克装置有许多诊断装置和系统,它们都需要同步为 10MHz 的全局实验时钟。我们从这个时钟信号中派生出 250MHz 的数据采集时钟,同时这个派生出的信号还为 ADC 板提供时钟。剩余的 FPGA 逻辑则由板载晶振时钟来驱动。

我们的系统有一个特别的地方,就是不会连续发送实验时钟,只在有触发事件的时候发送大约 10 秒钟。在此期间之外,我们需要切换到内部生成的时钟。因此我们需要在两个时钟之间来回切换,即在外部时钟和内部时钟间切换。

对两个 FPGA 板有一个重要要求,就是它们必须精确同步。在理想情况下,我们的采样周期为 4ns,那么在所期望的最高频率下 ADC 的可读输入正弦的周期为 8ns,相当于 360 度。如果我们需要 5 度的相位精度,我们能够容忍的最大歪斜为8X (5/360)=111ps。这种程度的精度很难实现,因为即便是光在这么短的时间内也只能行进 3.3cm。

我们为两块板子设计的固件完全相同。我们使用 DIP 开关来启用或者停用每块板子需要的不同功能。这样可以大幅度地节省开发时间,因为我们只需要对固件进行一次综合。

时钟由两块板中的一块生成,然后通过两个临近的 SMA 端口输出,随后反馈到与每块 FPGA 板的 FMC 端口相连的 ADC 板(使用相等长度的线缆)。这样可以保证每块板都能够精确地运行在相同的时钟上,唯一的相位差是信号离开 FPGA 板时两个 SMA 端口之间的相位差。图 4 更加清楚地说明了这种设计方法。