现场可编程门阵列 (FPGA) 是由通过可编程互连连接的可配置逻辑块 (CLB) 矩阵构成的可编程半导体器件。相对于专为特定设计定制构建的专用集成电路 (ASIC) 而言,FPGA 能通过编程来满足应用和功能要求。

虽然市面上也有一次性可编程 (OTP) FPGA,但绝大多数是基于 SRAM 的类型,可随着设计的演化进行重编程。

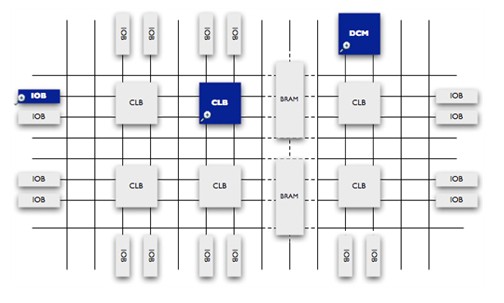

请参考下面的内容来具体了解方框图中的各个突出显示区域。

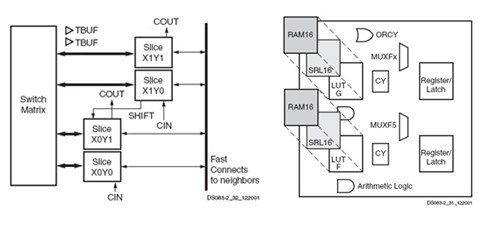

图1 FPGA 单元结构

IOB 细节

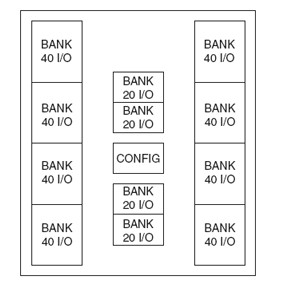

目前的 FPGA 可支持许多种 I/O 标准,因而为您的系统提供了理想的接口桥接。FPGA 内的 I/O 按 bank 分组 (见下图) ,每个 bank 能独立支持不同的 I/O 标准。 目前最先进的 FPGA 提供了十多个 I/O bank,能够提供灵活的 I/O 支持。

CLB 细节

可配置逻辑块是 FPGA 的基本逻辑单元。实际数量和特性会依器件的不同而改变,但是每个 CLB 都包含一个由 4 或 6 个输入、一些选择电路(多路复用器等)和触发器组成的可配置开关矩阵。开关矩阵具有高度的灵活性,经配置可以处理组合型逻辑、移位寄存器或 RAM。 这里给出了一个高层次的 CLB 简介。有关更多架构细节,敬请参阅相应器件的数据手册。