Policy Maker:关键性差异

在显示市场上,VESA通过 DisplayPort引领着从VGA、DVI以及HDMI等协议成功升级至高速串行收发器、基于包的层架构协议。与并行协议不同,串行分组协议在实现和维持连接或链路方面要多一层复杂性。在VESA DisplayPort 1.1a规范中,控制功能被划分为Link Policy Maker和Stream Policy Maker。Link Policy Maker可管理链路,并负责保持链路同步。其任务包括发现链路、对链路进行初始化和维护。Stream Policy Maker可管理传输初始化,并通过底层硬件对行动序列施加控制来维护同步流。

Policy Maker 的上述要素需根据特定的实施来决定,而且可在操作系统、软件驱动程序、固件或者FPGA逻辑中进行配置。为简化使用,许多商用DisplayPort IC将Link和Stream Policy Maker对设计人员隐藏。若用户显示要求与套装的DisplayPort ASSP相匹配,其价格和易用性无可争辩。但是,希望产品在竞争中脱颖而出的设计人员倾向于采用 FPGA。

Source Policy Maker参考设计

DisplayPort Source Policy Maker Controller System参考设计采用赛灵思MicroBlaze 嵌入式系统来实施与商用套装DisplayPort芯片类似的功能,且具备可进行源代码定制的额外优势。通过使用该参考设计的应用手册,用户不必对Policy Maker进行详细了解即可顺利启动设计工作,仅需简单地将范例设计连接起来。

除了上述源代码设计之外,DisplayPort的传输(Tx)或源端内核也配套提供了用于实现有限状态机(FSM)控制器的额外范例设计。

在显示市场上,VESA 通过 DisplayPort 引领着从 VGA、DVI 以及 HDMI 等协议成功升级至高速串行收发器、基于包的层架构协议。

DisplayPort Tx FSM 控制器范例设计(顶级文件名 dport_tx_fsm_cntrl)配套提供 DisplayPort LogiCORE 源端设计范例。此概念验证设计内含基于 RTL 的有限状态机,以实施可演示正确启动流程的简单 Policy Maker。dport_tx_fsm_cntrl 设计范例的优势在于可以显著缩短仿真时间。

Source Policy Maker Controller System参考设计采用MicroBlaze 嵌入式系统 XAPP,其顶级 ISE项目名称为“dport_source_ref_design.xise”。它使用户能够根据自己需要对 Source Policy Maker Controller 的源代码进行修改。此外,还能够与LogicCORE v1.2 (IDS 12.1) 和 Spartan-6 TED 消费类视频套件协同运行。

上述两种范例设计均包含可实现内核设置及链路和流维护的基本流程。

功能概述

源端、宿端/视频规范都会采用 Policy Maker,但在 DisplayPort LogiCORE 中,赛灵思对它们进行了差别实施。与源(发送)端的 Policy Maker 功能相比,宿(接收)端的 Policy Maker 功能要简单得多。赛灵思在 LogiCORE 内实施了大部分宿端 Policy Maker 功能。基于 RTL 的宿端控制器可提供剩余部分的功能。由于源端 Policy Maker 的功能复杂得多,因而可采用源代码参考设计的方式提供。

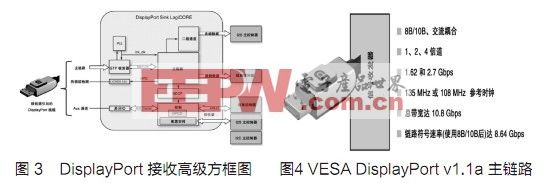

让我们来深入了解源端 Policy Maker,其使设计人员能够最大限度地提高功能灵活性与实施灵活性。顶级范例设计包含内核的两个高级组件示例:XAPP 使用 MicroBlaze 嵌入式系统实施 DisplayPort Source Policy Maker Controller System参考设计;以及 DisplayPort 内核源端(发送)设计。赛灵思将内核的实施分成原子链路功能,分别称为主链路、二级通道以及 AUX 通道协议。主链路可实现主视频流的交付。二级通道可在消隐期内将音频信息的交付集成到主链路中。赛灵思将在未来的内核中提供二级通道。同时,AUX 通道可为宿端通信通道建立专用源端(见图 2)。

赛灵思为用户数据接口新增了线路缓存器,使用户能够在 FPGA(见图 2、3 和 4)中便捷实施范例设计。图 3 中宿端的 Policy Maker 与 Device Controller 都是 CORE GeneratorTM 所提供宿端设计范例的组成部分。

MicroBlaze 处理器发挥核心作用

赛灵思推出的Source Policy Maker Controller可与内核配合使用,这样其功能在很大程度上和ASSP DisplayPort源端设备一样。建议您使用MicroBlaze嵌入式或外部处理器来正确初始化和维持该链路。XAPP包含的Policy Maker参考设计预配置版本在FPGA内的 MicroBlaze 处理器中实施,可帮助用户立刻将设计方案转换成硬件。正式供货时的参考设计将包含设计人员可修改的源代码。