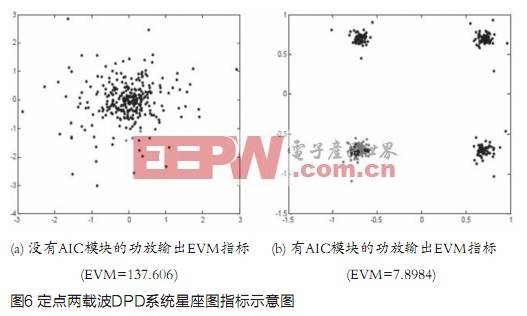

其次,通过量化指标EVM进行比较[3],图6给出了信干比为-10dB时的EVM指标,可以看出,AIC算法可有效抵消干扰,改善星座图。

硬件测试说明

在硬件实现时,利用的开发平台为Virtex II Board。其中V2P30芯片FPGA具有136个硬核乘法器和块RAM,可满足自适应滤波算法以及大点数的FFT变换需要大量的乘法器和存储器的需求。此外,大量的Slice可实现小区搜索模块以及相关测试平台的建立。

此外,对于简易的视频测试平台,利用VGA接口完成测试平台,进行最终的测试验证。XUP Virtex II PRO板卡带有高精度的DAC芯片FMS3818,能达到预期目的。软件开发选用了ISE8.2.03i,相应的Chipscope为8.2版本。

硬件系统需要实现频域AIC、小区同步搜索、WCDMA信源发生器、测试平台4大模块。其中AIC模块可划分为大点数的FFT变换以及相应的串并、并串转换等主要功能。将设计分为5个大的模块:顶层模块、AIC处理模块、信源发生器、小区搜索以及测试平台。FFT模块利用赛灵思公司的IP Core(知识产权核)来完成;串并、并串可以利用块RAM实现;数据处理模块尽可能地使用SRL16结构来实现,以节省资源。

系统测试按照由部分到整体的思路来完成,首先对各个模块进行单独测试,再将部分模块组合起来完成测试,最后再对整体系统进行测试。这样,可以将错误及早发现并将其消灭在起步阶段。测试主要依靠ChipScope来完成,利用其采集数据,再把数据导入MATLAB中,和定点仿真、ModelSim输出结果进行比较,完成数据分析,从而确保芯片的运行结果和仿真结果是相同的。在测试中,全部以方波测试平台为基准。

参考文献:

[1]Widow B, et al, Adaptive noise canceling: principles and applications, Proceedings of the IEEE. 1975,63:1692-1716

[2]Shankar S. Transform Domain LMS Algorithm, IEEE Transactions on acoustics, Speech, and Signal processing. 1983, ASSP-31(3)

[3]田耘,徐文波,等.无线通信FPGA设计[M].北京:电子工业出版社,2008

[4]Haykin S. Adaptive Filter Theory[M].北京:电子工业出版社(影印版),2002

[5]3GPP,TS 25.101,V4.0.0,UE Radio Transmission and Reception (FDD), 2001