赛灵思编译器支持的 APU-FPU 单精度变量使用的资源较少。当 FPU 被占用时,双精度操作将通过软件仿真来执行。

软 FPU 比软件仿真法平均快 6 倍。单精度 FPU 通常比双精度快 13%

将 APU-FPU 连接至 PowerPC 440

有两种方法可将 APU-FPU 连接至 PowerPC 440 处理器:1、利用赛灵思 Platform Studio 设计工具中的 Base System Builder (BSB) 向导;2、将 APU-FPU 单元添加至当前设计方案中即可。

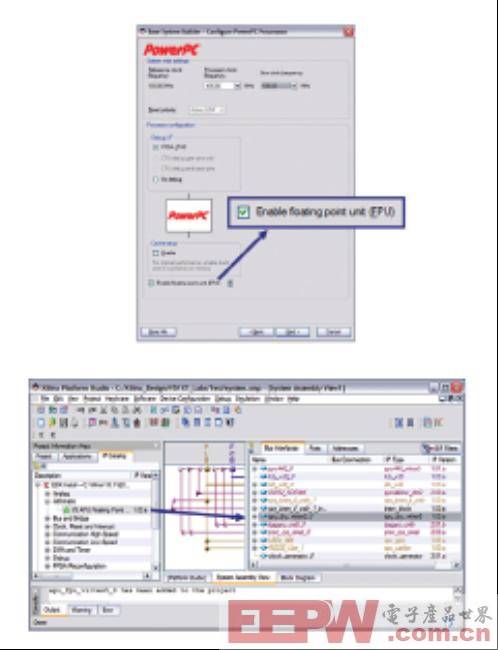

您首先需利用 BSB 向导确定目标板和所期望的处理器(PowerPC 或 MicroBlaze™),然后通过一系列复选框和下拉菜单选择设计中所需的 IP。借助 BSB 向导,能够轻松快速地组装并测试基础处理器系统。您只需勾选您要选择的 FPU 框,即可实现APU-FPU 连接(见图 3 顶部)。该向导可实现一个经过优化能以处理器时钟三分之一速率运行的双精度 FPU。您也可定制更高时钟速率的 FPU 和单精度 FPU。

如果不想使用向导,您也可通过另一种方法来实现,即按照系统组装视图拖动 IP Catalog 下的 APU- FPU IP,然后对 FPU 进行配置即可。图 3 底部图片显示了 IP Catalog (见左下方)和系统组装视图中新添加的 FPU。右击 FPU 并选择 Configure IP,然后您便可选取想要的精度(单精度或双精度)并确定您希望该 FPU 是针对低时延(三分之一时钟速率)或是高速率(二分之一时钟速率)而进行优化;最后将 FPU 连接至 FCB 并将 FPU/FCB 时钟链接至适当的时钟(通常是二分之一或三分之一处理器时钟速率。)

图 3——通过 BSB 向导(顶部)以及系统组装视图将 FPU 添加至现有 PowerPC 处理器设计方案中