PowerPC 440 Processor Block: PowerPC 440 处理器模块

PowerPC 440 Processor: PowerPC 440处理器

PLB and Memory Crossbar: PLB 和存储器交叉开关

Virtex-5 APU Floating-Point Unit: Virtex-5 APU 浮点单元

in FPGA Logic: FPGA 逻辑内

关于 PowerPC 440 FPU

赛灵思针对嵌入在 Virtex-5 FXT FPGA 中的 PowerPC 440 处理器专门设计了 APU-FPU。FPU 通过 APU 接口与处理器的紧密结合可让浮点运算单元直接执行原生 PowerPC 浮点指令,这相对软件仿真而言,速度一般可提高 6 倍。

除少数情况外,赛灵思 PowerPC FPU 一般符合单精度和双精度浮点运算的 IEEE-754 标准。赛灵思提供了为 2:1和 3:1 APU-FPU 时钟速率而优化的变量,使 PowerPC 处理器能够以最高频率运行。自发性指令发送不仅会隐藏运算时延,而且还会减少每条指令的周期。此外,这些优化的实施方案可充分发挥器件的高性能 DSP 特性,以缩短运算符时延并减少逻辑计数与功耗。赛灵思在其嵌入式开发套件 (EDK) 中支持 APU-FPU 流。

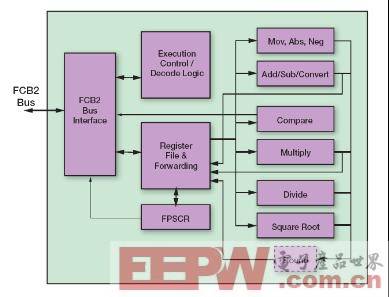

图 2 为 FPU 架构的整体框架图。APU-FPU 由执行单元、寄存器文件、总线接口以及所有管理浮点指令执行情况所必需的控制逻辑组成。

FCB2 Bus: FCB2 总线

FCB2 Bus Interface: FCB2 总线接口

Execution Control/Decode Logic: 执行控制/解码逻辑

Register File & Forwarding: 寄存器文件与转发

Add/Sub/Convert: 添加/子集/转换

Compare: 比较

Multiply: 乘

Divide: 除

Square Root: 平方根

Round: 四舍五入

图 2——Virtex-5 FXT PowerPC 440 浮点协处理器架构

FPU 含有两个变量。双精度变量可执行除 PowerPC ISA 图形子集(fsel、fres 和 frsqrte)以外的所有浮点指令,其中也包括单精度变量执行的指令。这意味着您能使用带各种商用编译器和操作系统的 FPU(具体请参见:www.xilinx.com/ ise/embedded/epartners/listing.htm)。