2 系统硬件电路设计

如图4所示,系统硬件由两大部分组成,分别是虚线框内的采样电路部分和开发板部分[6-7]。本文采用的Spartan-3A DSP 入门级开发板是Xilinx公司出品的基于Spartan-3A DSP FPGA设计的一个开发平台。采样电路实现对三相电压、电流的整周期同步采样,其设计尺寸与Spartan-3A DSP开发板相同,通过EXP接口实现与开发板的通信。它包括:电压、电流互感器、调理电路、低通滤波电路、锁相倍频电路、AD转换器及电平转换电路。

3 硬件联合仿真与结果分析

3.1 硬件联合仿真

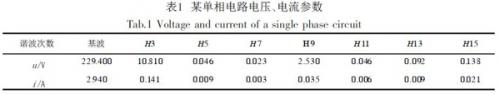

由于实验条件所限,本文采用的是单相220V的市电为检测对象。接入额定电压220V,标称功率800W的电加热器为负载。首先用FLUKE434型电能 质量分析仪检测出该负载上的电压、电流的各次谐波参数,如表1所列,其电压总谐波畸变率THDV=4.9%,电流总谐波畸变率THDI=4.8%。

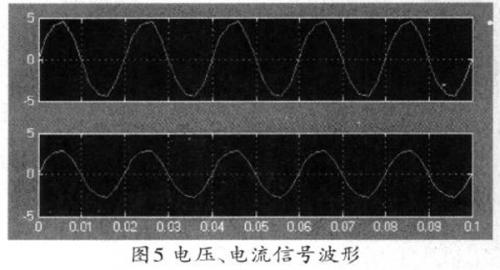

经采样后得到的数字信号量在0~5V之间,依照给定参数分别乘系数J、K,利用Simulink中模块生成一组表征电压、电流的数字信号作为系统的输入信号。如图5所示。

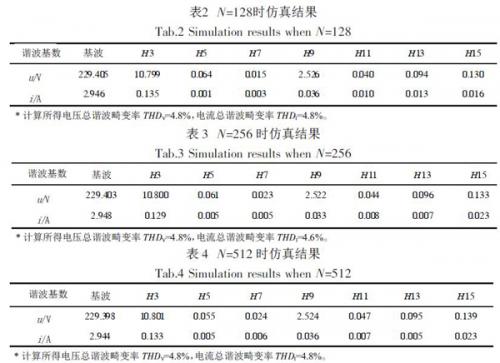

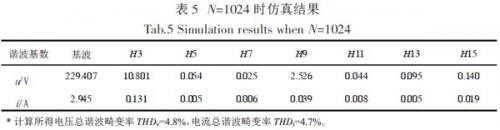

将FFT模块中的采样点数分别设置成为128、256、512、1024,并设置相应的采样频率,然后运行硬件联合仿真模型;将计算结果再乘系数1/J、1/K,得到表2~表5所示结果。

3.2 仿真结果分析

由各表中可以看出,计算出的幅值以及根据幅值计算所得总谐波畸变率的误差都比较小。随着采样点数的增加,计算所得基波和较低次数的谐波幅值的误差和总谐波 畸变率的误差并没有明显减小,而次数较高的谐波误差减小较明显。究其原因,N点FFT计算可以分解出0~N/2-1次谐波,N=128时就可以分解出63 次以内的谐波了。而对于次数较高的谐波,采样点数的增加对其幅值误差的改善还是比较明显的。硬件实现时,在计算精度满足要求的情况下,考虑到实时性的要 求,可选用256点FFT进行计算。

此外,计算所得相位出现了很大的偏差;原本设想通过改变待测信号参数,分析仿真结果来推导出相位偏差的规律,但是随着数值的改变,相位偏差规律并不 明显,并未达到预期目的。然而,在改变信号参数的分析过程中发现,相位的改变对谐波幅值和总谐波畸变率的计算并没有太大影响,计算精度基本满足要求。因 此,实际硬件实现时,舍弃掉相位计算,只计算出各次谐波的幅值及总谐波畸变率。

4 结束语

本文提出了一种采用基于Xilinx FPGA 实现FFT算法的电压、电流谐波检测的模块化的设计方法。使用System Generator设计了谐波检测的模型及前端采样电路,并以Spartan-3A DSP开发板为平台进行了硬件联合仿真验证。