随着嵌入式处理需求的快速增长,系统架构正朝着多处理器设计的方向发展,以解决单处理器系统复杂度太高和计算能力不足的问题。凭借其高逻辑密度及高性能硬模块,新一代FPGA已经使功能强大的芯片多处理(CMP)解决方案成为现实。目前的挑战在于如何在该解决方案的范畴内快速完成设计的开发与创建。

赛灵思嵌入式开发套件(EDK)工具和IP具有很大的灵活性,用户可以利用它们以FPGA逻辑为基础设计出独具特色的定制多处理解决方案,从而同时满足价格和性能目标要求。本文将主要介绍以PowerPC和MicroBlaze嵌入式处理器为基础的赛灵思解决方案中的多处理概念。

应用领域

性能和功能划分是设计多处理器系统的主要动力。总的来说,多处理在以下这些常见场合中会发挥作用:

1. 多个独立功能。设计可能需要应对多个独立的处理任务。解决这个问题的好方法是为每个处理任务创建独立的专用处理模块,并为每个处理模块分配专用处理器和外设集。

2. 控制或数据层面卸载。常见情况是既有实时任务(计算或数据密集型),也有非实时任务,从而可能导致单处理器解决方案无法做出及时的响应。对于这种情况,您可以分配一个从处理器以便及时完成实时任务,主处理器则完成其他常规任务,并且充当到主机系统的接口。主处理器同时也监控从处理器。从处理器可能包含专用功能或接口,从而能够满足计算性能要求。相应的例子包括网络负载分担、媒体处理以及安全算法等。

3. 接口处理。对于作为多接口之间的桥梁或开关的系统,您可以分配一个从处理器用于处理每个接口上的数据,而用一个或者多个主处理器处理更高级的桥接或者开关任务。

4. 数据流处理。对于数据流计算问题,您可以安排多个处理器以流水线的方式处理数据流。多处理器流水线的每一级都要在将数据传到下一个处理器之前完成一部分计算任务。这是提高系统吞吐量的一种有效方式。

5. 可靠性和冗余度。您可以多次复制处理系统以提高可靠性和冗余度。

6. 对称处理。传统的对称处理(SMP)是一种十分有用的解决方案,您可以利用它来提升那些不存在明确划分边界的应用性能。一个具有SMP功能的OS层可以管理并行任务,并且在多处理器之间自动调度这些任务。然而,SMP使用模型不适用于赛灵思处理器,因为它们缺乏实现SMP所需的高速缓存相关性。

除了SMP场合,其他的所有应用场合均适合赛灵思公司带有EDK工具的FPGA的应用。赛灵思处理解决方案的独特之处在于,它可以针对应用要求来灵活定制每个处理子系统。例如,并不是所有的处理器都需要一个高速缓存或者浮点单元。通过为特定处理器分配特定的功能,您可以创建一个能够实现所有设计目标的专用解决方案。

简单且可扩展的系统架构

正如您见到的那样,有许多种使用模型适合多处理器使用。同时存在多种系统架构的可能性。为某一应用场合明确一种单纯且可扩展的拓扑和架构是一件令人头疼的事情,所以定义一个可以满足大部分需求的基线架构会将有所帮助。

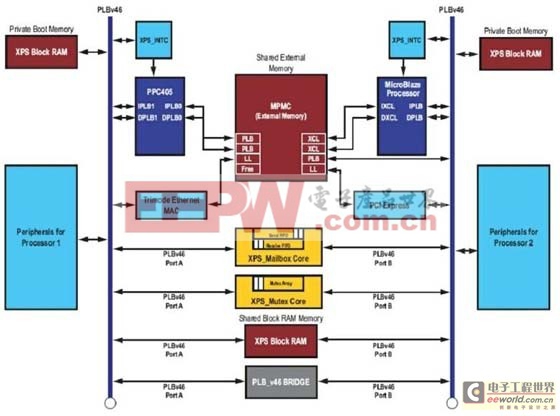

图1给出了一个双内核架构。这个架构展示了简单且可扩展的多处理器系统定义。您可以基于这个定义衍生出新的拓扑来应对设计约束或挑战。该架构的主要概念如下:

图1:双处理器架构