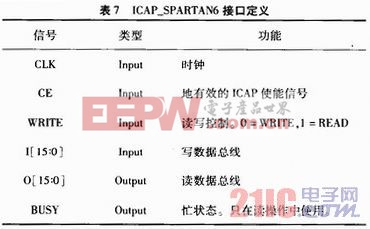

在主SPI模式下,ICAP_SPARTAN6的输入数据在从总线I[15:0]输入前,要进行字节范围内的位交换,即16位宽的字分为高8位1 Byte,低8位1 Byte,各字节的最高位[7]和最低位[0]交换,位[6]与位[1]交换,其他以此类推。

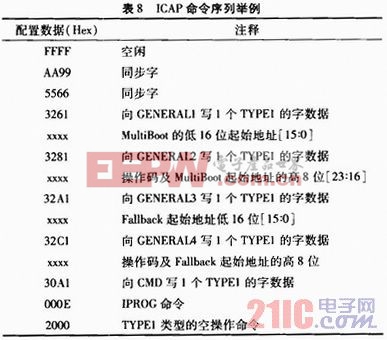

通过ICAP触发IPROG的命令序列举例如表8所示。

IPROG命令后需经过一段时间后,FPGA内部才会产生相应的重配置信号,因此在IPROG命令后需跟几个空操作命令,一般为4个。GENERA L2、GENERAL4中的操作码:0x0B、0x3B、0x6B分别为SPIx1、SPIx2、SPIx4。

ICAP逻辑模块是FPGA中的专有逻辑模块,因此在生成bit文件的各源文件中必须都实例化一个ICAP模块。一般情况下对ICAP模块的控制操作通过状态机实现。

4.2 选项设置实现

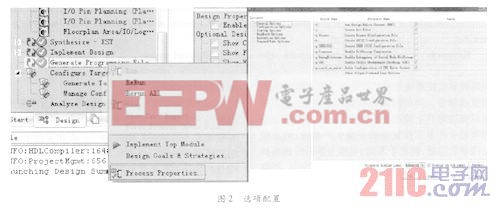

实现MultiBoot功能所需配置的所有寄存器,均可在生成bit文件时通过添加相关的生成设置选项实现。在进程菜单中单击Generate Pro gramming File,选择Process Properties,弹出配置窗口如图2所示。

5 结束语

介绍了实现MultiBoot操作的两种方式,一种是基于ICAP的寄存器编码配置方式。可通过源代码中的注释,使后续开发维护人员阅读代码、扩展功能时思路清晰,缺点是需编写大量代码,并需对ICAP的操作与命令序列有一定了解。第二种通过在生成bit文时添加相关设置选项实现,方便简单,但需大量的文本注释,以便后续的开发与维护。当然,实际的应用开发过程中可同时使用这两种方法,实现更高效便捷的编码开发。