OpenCV是一款具有行业标准、包含OpenCV.org算法的开源库,能帮助嵌入式视觉开发人员快速创建视觉系统。全球嵌入式视觉开发人员积极地为这款开源库开发新的算法,目前已经包含了2500多款使用C、C++、Java和Python语言编写的算法。库中的算法具有各种不同的复杂程度,有的可执行图形滤波器等简单功能,有的则能执行运动检测等更高级的分析功能。赛灵思的视频技术设计总监Alvarez表示,这些OpenCV算法可用于微处理器和DSP等处理器的实现,支持Intel、ARM、Nvidia、MIPS/Imagination Technologies、TI等不同厂商的产品。由于Zynq-7000 All Programmable SoC采用ARM处理系统,因此用户能在Zynq-7000 All Programmable SoC的处理器上实现这些采用C++语言编写的算法。

Alvarez指出,有了Vivado HLS,用户可以用C或C++语言编写这些算法,将函数调用从OpenCV改为HLS,并使用Vivado HLS将这些算法综合或编译到RTL代码,从而针对Zynq-7000 All Programmable SoC逻辑部分的实现进行优化。Vivado环境中提供OpenCV,能让Smarter视觉架构设计人员方便地比较设计方案中的给定算法到底是在处理器还是Zynq-7000 All Programmable SoC的FPGA逻辑部分运行效率最佳。赛灵思开源库的推出可为客户提供一个良好的设计开端。就Vivado HLS而言,赛灵思已经编译了OpenCV库中30多种最常用的嵌入式视觉算法。客户可在系统级快速权衡处理器与逻辑,而且能立即在Zynq-7000 All Programmable SoC上运行,确保给定应用实现最佳的系统效果。

赛灵思及其联盟成员还将积极从OpenCV库持续进行功能移植,每个季度都将向赛灵思不断扩展的用户群提供新的功能。由于开发人员能在几乎任何商业处理器上运行OpenCV库,因此视觉设计人员能比较各种芯片器件上运行的不同算法的性能,甚至明确性能基准。赛灵思坚信,广大客户必将发现Zynq All Programmable SoC的明显优势。事实上,您也可在本演示中见证Zynq-7000 All Programmable SoC和赛灵思Smarter Vision技术的强大实力。赛灵思杰出工程师Kees Vissers在演示中将介绍如何使用OpenCV算法,并配合使用Vivado HLS快速在Zynq-7000 All Programmable SoC的FPGA逻辑部分实现这些算法,而相对于在ARM A4处理子系统中实现相同功能而言性能可提升50倍到100倍之多。

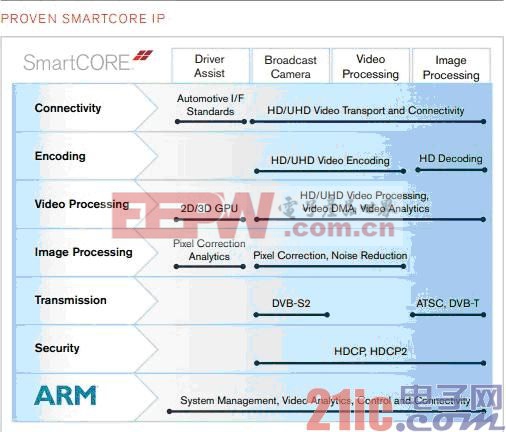

赛灵思的SMARTCore IP产品系列能充分满足各种不同细分市场对于高级Smarter Vision系统的必要要求。

作为Smarter Vision计划的一部分,赛灵思还推出了SmartCORE IP组合,以满足各种细分市场的Smarter视觉设计要求,为新一代产品带来Smarter视觉功能。客户能通过使用赛灵思新推出的IP Integrator工具在其设计中快速实现SmartCORE IP组合的内核以及OpenCV库的算法。这款新工具是一种新型即插即用IP环境,能帮助用户在原理图环境中工作,或者如果需要的话也支持在命令行环境中工作。

Alvarez指出,自Vivado设计套件诞生后,赛灵思让该套件的设计具有器件意识,这样就能充分发挥每款器件的功能。Alvarez称,有了IP Integrator,Vivado设计套件不仅具有器件意识,现在还具有目标平台意识,支持所有Zynq All Programmable SoC和7系列FPGA开发板以及套件。具有目标平台意识,就意味着Vivado设计套件现在能配置和应用特定开发板的设计规则检查,从而确保快速推出切实可行的系统。

举例来说,当设计人员选择赛灵思 Zynq-7000 SoC视频及成像套件,并在IP Integrator中实例化Zynq-7000 All Programmable SoC处理系统时,Vivado设计套件则会用正确的外设、驱动程序和存储器映射对处理系统进行预配置,从而为开发板提供支持。嵌入式设计团队现在能面向双核ARM处理系统和高性能FPGA逻辑更迅速地识别、重用并集成IP软/硬核。

用户可通过一系列对话框指定处理系统及其逻辑之间的接口。IP Integrator随后自动生成RTL并针对性能或占用面积进行优化。接下来用户能添加自己的定制逻辑,或用Vivado IP目录完成设计。

我们非常高兴看到赛灵思的客户迄今为止使用赛灵思FPGA推出了那么多出色的Smarter Vision系统。赛灵思更加期待看到客户使用Zynq-7000 All Programmable SoC和强大的Smarter Vision环境推出更出色的产品。鉴于过去大家已经取得的出色成绩,我们相信未来一定会更加美好!