基于Xilinx FPGA的片上系统无线保密通信终端

来源:网络 时间:2011-04-19 浏览量:2886

3.3 软核控制模块

3.3.1 软核MicroBlaze简介

MicroBlaze 是一款由xilinx公司开发的嵌入式处理器软核,其采用RISC(Reduced Instruction Set Computer)优化架构。它符合IBM CoreConnect标准,能够与PPC405系统无缝连接[3]。MicroBlaze是一个非常简化却具有较高性能的软核,在Spartan3E系列FPGA中它只占400个Slice,相当于10万门FPGA容量的1/3。其为哈佛结构,32位地址总线,独立的指令和数据缓存,并且有独立的数据和指令总线连接到IBM的PLB总线,使得它能很容易和其它外设IP核一起完成整体功能。支持SPI、I2C、PCI、CAN总线,支持重置、硬件异常、中断、用户异常、暂停等机制,可配置UART、GPIO等接口。

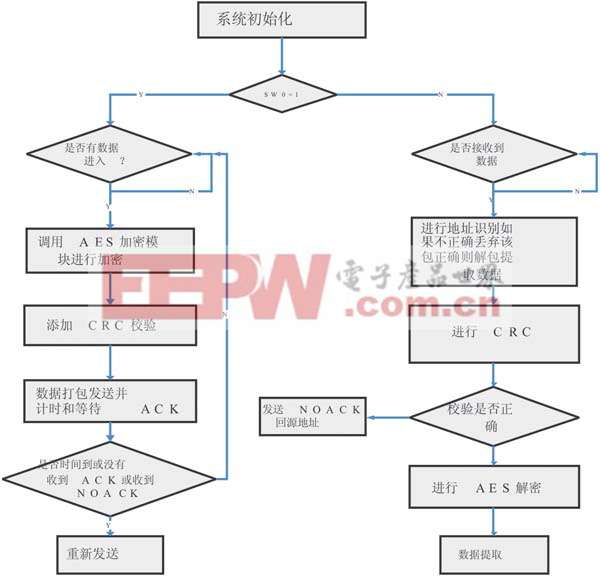

3.3.2 microblaze的控制流程

图3 microblaze的控制流程

3.3.3 microblaze的控制流程主程序

main () {

Initial()//初始化系统;

CmdSend()//上位机命令输入;

DataRev()//数据接收;

AESEny()//数据加密;

DataPackage()数据打包;

CC2420Sen()加密数据发送;

Return success; }

结语

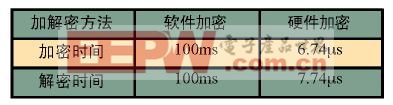

本系统将软件加解密(在50M的频率下使用软件来进行加解密)与硬件加解密时间做了对比:如表3所示。

表3 软件和硬件加密对比

表4 AES加密占用FPGA资源统计表

该方案充分有效的利用了Spartan 3E的资源,尤其为可编程逻辑和RAM的利用。其中AES加解密中的乘法运算均由LUT查找表来实现,用空间换取时间,获得了很高的算法速度。在AES算法测试时我们发现80%的AES加解密时间都用于密钥扩展算法中,如果能再进一步把算法优化,比如做成流水线的算法模式的话,加解密时间又能减少近20%,即由现在的6.74us减少到略大于5.39us,效率又可以增加很多。

参考文献:

[1]AES算法FPGA实现分析,唐金艺,[M] 海军计算技术研究所

[2]唐明,张焕国,刘树渡等 AES的高性能硬件设计与研究 [M] 武汉大学计算机学院

[3]赵峰 马迪民 孙伟等 FPGA上的嵌入式设计[M] 2008.4

[4]佟玉伟 陆浪如 FPGA先进加密算法 (AES) 的并行实现 [M] 交通与计算机 2002.6