FPGA是通过逻辑组合电路来实现各种功能的器件。由于FPGA内部集成了大量的逻辑资源和可配置的I/O引脚,加上独特的并行处理架构,可以轻松实现同时对多个外部设备的配置和管理,以及内外各种接口数据的传输。现在开发厂商又在FPGA 内部加入了大量的DSP和Block RAM资源,非常适合图像处理、数字信号处理等运算密集的应用,因此在这些领域取得了广泛的应用。但是由于FPGA 程序编写的灵活性和功能的多样性,使得它在一个复杂工程中对各个程序的使用调度、统筹管理上有很大的局限性,这样就必须引入操作系统进行统一的管理。Linux 系统则因为其良好的可裁减、可配置等特点在嵌入式领域应用广泛。 Linux操作系统提供了许多系统级的应用,例如网络协议的实现、进程调度、内存管理等,同时Linux 是一个成熟的开源操作系统,有丰富的应用资源,利用这些资源和强大的系统功能,用户可以快速地开发基于嵌入式环境复杂系统。因此,结合FPGA和Linux双方优势,可以很好地满足嵌入式系统设计需求,量体裁衣,去除冗余。本文给出了一种基于Xilinx FPGA的嵌入式Linux操作系统解决方案。

基于FPGA的嵌入式系统的硬件设计

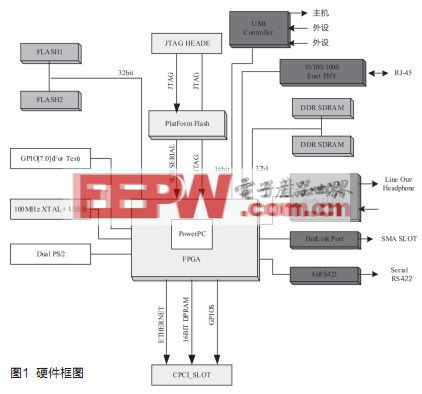

本设计是基于Xilinx XC4VFX40系列 FPGA,它内部集成了两个PowerPC405处理器, 4个10/100/1000M以太网MAC模块,运行频率300MHz时,具有420D-MIPS性能,能解决高速网络数据传输问题,并且能解决通过网络加载操作系统和交叉编译等问题。它内部有448个可配置I/O口,2592kb BlockRAM,能实现对各种外部设备的并行控制以及较多数据的存储与处理。加载一个操作系统,一般需要几十兆的内存空间,FPGA内部自带的RAM空间是远远不够的,本设计在板上扩展了两片MICRON公司的256Mb DDR内存,作为上电时操作系统的加载和运行空间。现在主流的嵌入式操作系统,都需要搭建交叉编译环境,把在主机上编写好的可执行文件下载到目标板上,这就需要实现网络数据的传输。由于XC4VFX40 自带了以太网MAC模块,只需要在外面添加个PHY芯片和带隔离器的RJ45接口就能实现这个功能。本设计由于对网络数据实时性要求很高,因此采用Marvell公司的千兆以太网PHY芯片88E1111-RCJ。它能根据自身配置和主机设计,实现10/100/1000M自适应传输,并且Linux本身对这个芯片提供了驱动支持,实现无缝链接。操作系统加载到DDR 中能快速有效的运行,但是掉电就会丢失,因此必须加入FLASH芯片,把系统文件存储到外部FLASH中。加电时,FPGA把操作系统文件从FLASH读入到 DDR中运行。FPGA设计当然会扩展很多接口出来,利用自身并行处理的优势,控制很多外围设备,本设计也不例外,扩展了8个通用的GPIO,2个PS/2接口,1个USB接口,1个AC97声卡接口,1个 HotLink接口,以及4个RS422接口,同时扩展了两个CPCI接口,引出了16位数据地址线和Ethernet控制线,整个系统的硬件框图如图1所示。

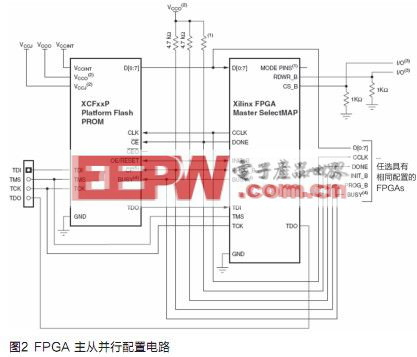

在进行电路设计时,是以FPGA为核心,向外扩展各种设备,因此特别注意了FPGA各个引脚的连接。由于DDR和PHY芯片都需要提供+2.5V电压,因此和DDR、PHY芯片连接引脚所在的BANK需要提供+2.5V电压参考,并且不能接以LVTTL或LVCMOS为电压参考的引脚。重要快速的时钟信号必须接到全局时钟引脚上。由于FPGA需要通过外部FLASH启动操作系统,需要并行配置,以减少加载时间,配置电路如图2所示。在DDR布线时,数据和地址线需要走等长线,数据线之间不能相差10Mil,地址线要控制在20Mil以内,时钟也需要走差分等长线,长度应大于地址线,DDR各个信号还需要47Ω的并行端接,改善信号质量。千兆 PHY 输出MDI信号也需要在顶层做差分等长,不然在进行1000M数据传输时很可能不稳定。DDR和PHY需要完整的电源回路做参考,电源层划分时也要特别注意,其他电路做常规处理就可以了。

EDK和ISE软件设计

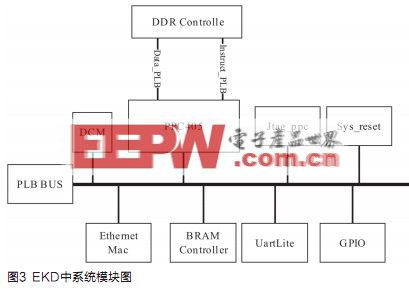

首先需要调用Xilinx提供的 EDK软件,对各个模块加入必要的IPCORE,以便操作系统能正常调用这些器件的驱动操作他们。本设计采用的是EDK10.1.2版本,PPC方面选用ppc405内核,频率设定在300MHz,同时需要添加中断输入引脚,以便响应以太网、串口等外部中断,其他使用默认设置。DDR控制器采用EDK提供的Multi-Port-Memory Controller模块,需要设置DDR芯片厂商、大小和数据位数等,特别指出的是,要设置独立的两条PLB总线和PPC连接,作为PPC的指令和数据总线。MAC单元需要加入XPS_LL_TEMAC模块来控制,本设计需要设置PHY 类型为GMII(千兆以太网),同时要指定物理地址和收发FIFO大小。FLASH单元需要加入xps_mch_emc模块,同时设置FLASH类型和读写时间。为了方便调试,还需要加入串口控制台模块,本设计使用的是UartLite模块,设置需要的波特率和校验类型。特别注意的是,系统还需要时钟管理模块(DCM),提供各个模块需要的不同时钟,还要设置一段FPGA内部RAM区域,放置PPC的.boot文件。外部这些模块都通过PLB总线和PPC通信,需要统一编址,一般把DDR 内存空间地址分配到0x0开始,整个系统的构建如图3所示。