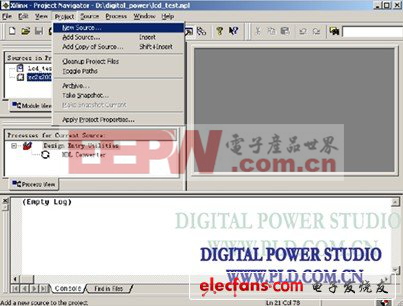

如图 7 中所示,在 Project 菜单下,选择 New Source 建立新的代码文件。弹出的对话框如图 8 所示。

图7 Project 菜单

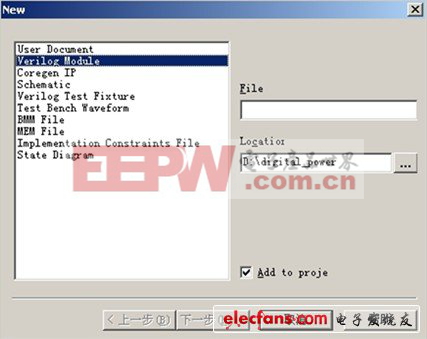

图8 新建代码文件对话框

在 File 中输入文件名称,Location 最好选用和 project 文件所在目录同一个目录。将 Add to project 选单选中,该文件将自动被加入当前 project 中。在左边窗口中选择建立的文件类型,如图 8 选为 Verilog Module。点击下一步,如图 9所示。

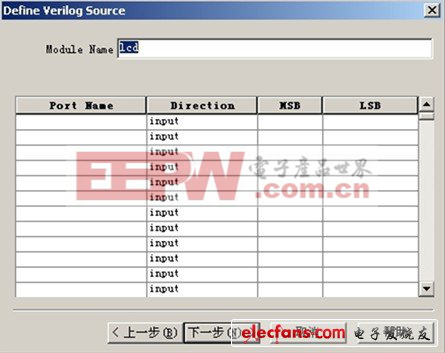

图9 Verilog 代码文件定义对话框

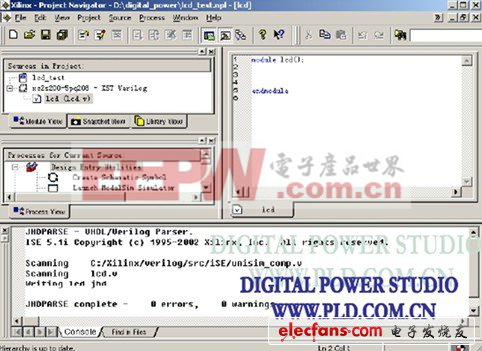

在图 9 中,可以定义代码文件的输入输出端口,可以不进行定义,直接点击下一步。如果进行了定义的话,生成的代码文本文件会自动加上定义好的输入输出端口。点击下一步,进入下一对话框后点击完成,即可。如图 10 所示。在图10 中,可见左面 Module View 中 project 中已经多处了刚才建立的 lcd 模块,右边打开的 lcd 文件界面中,可以进行代码的编写。

图10 代码文件生成后界面

前面介绍的是编写代码,如果已经用其它工具编写好了代码,或者有现成的代码,则不需要再重新编写了,下面介绍如何将已有的 verilog 文件导入到 project中。

在图 7 中不要选择 New Source,而选择 Add Source。在弹出的窗口中找到已有代码文件(可同时加多个文件),并点击“打开”即可。注意:Add Source 是将当前选择的代码加入到当前 project 中,而 Add Copy of Source 是将代码文件复制到当前 project 所在目录中,并将复制后的文件加到 project 中。建议使用后者。添加后结果如图 11 所示。(在本文例子中,加入的是 Digital Power 提供的液晶程序 lcd.v。)可以看到在Module View 窗口中将显示出 verilog 代码中所有Module,并显示出其层次结构以及其所在的文件。

图11 Add Source 结果图

3.调用 Modsim 进行仿真

由于 modsim 的性能非常优秀,以及它的普及程度广,在本文中,介绍如何调用 modsim。首先,在 edit 菜单中选择 Preferences 选项,弹出如图 12 所示对话框。在 Partner Tools 中的 Model Tech Simulator 输入框中填入您所安装的 Modsim 应用程序文件的路径。若您所装的 Modsim 版本为专门为 Xilinx 编写的 Modsim Xilinx

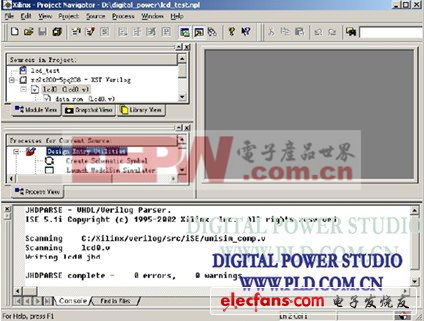

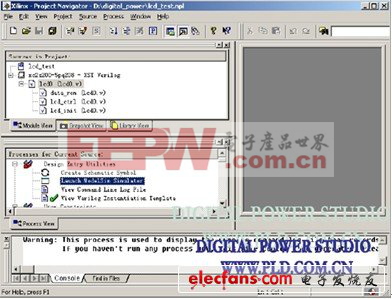

edition版本,可以省略该步骤。经过设置以后,回到如图 13 所示界面。

图12 Preferences 对话框

图13 调用 Modsim