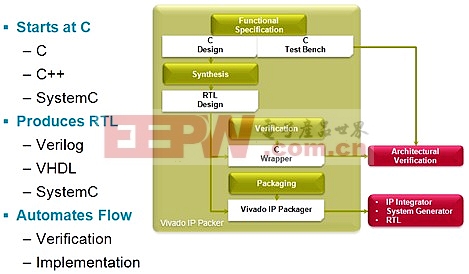

在这个流程中,用户先创建一个设计 C、C++ 或 SystemC 表达式,以及一个用于描述期望的设计行为的 C 测试平台。随后用 GCC/G++或 Visual C++ 仿真器验证设计的系统行为。一旦行为设计运行良好,对应的测试台的问题全部解决,就可以通过 Vivado HLS Synthesis 运行设计,生成 RTL 设计,代码可以是 Verilog,也可以是 VHDL。有了 RTL 后,随即可以执行设计的 Verilog 或 VHDL 仿真,或使用工具的 C封装器技术创建 SystemC 版本。然后可以进行System C架构级仿真,进一步根据之前创建的 C 测试平台,验证设计的架构行为和功能。

设计固化后,就可以通过 Vivado 设计套件的物理实现流程来运行设计,将设计编程到器件上,在硬件中运行和/或使用 IP 封装器将设计转为可重用的 IP。随后使用 IP 集成器将 IP 集成到设计中,或在系统生成器 (System Generator) 中运行 IP。

这只是使用该工具的方法之一。实际上在即将发行的赛灵思Xcell杂志中,安捷伦的 Nathan Jachimiec 和赛灵思的 Fernando Marinez Vallina 将介绍如何使用 Vivado HLS 技术(在 ISE设计套件的流程中称为 AutoESL 技术)为安捷伦开发 UDP 包引擎。

VIVADO 仿真器

除了 Vivado HLS,公司还为该套件新开发了一种同时支持 Verilog 和 VHDL 的混合语言仿真器。Feist 表示,只需要单击鼠标,用户就可以启动行为仿真,然后从集成波形查看器中查看结果。通过采用最新性能优化的仿真内核,可加速行为级仿真速度,执行速度比赛灵思 ISE 设计套件仿真器快三倍。采用硬件协仿真,门级仿真速度则可加快 100 倍。