对所有的嵌入式系统来说,必然会在一定的设计阶段进行决策,决定对给定的应用到底是选择ASSP 还是采用合适的片上系统 (SoC) 解决方案。这两种选择都需要交替使用并进行折衷。如果选用 ASSP,虽然它是一款便于实施的标准现成解决方案,但对许多新型应用来说,会严重阻碍设计团队的产品定制与差异化能力的发挥。毫无疑问,用 FPGA 或 ASIC 从头开始构建 SoC 可以实现终极定制。尽管一些设计团队能证明构建 ASIC 是合理的,但是越来越多的OEM厂商利用 FPGA,从成本、功耗、密度和性能角度而言提供与ASIC相同的功能,但是风险却大大降低了。

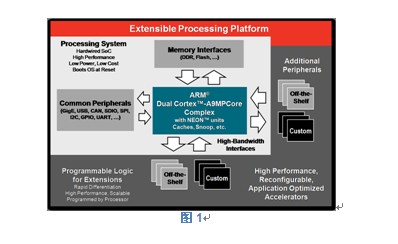

赛灵思可扩展式处理平台的推出,意味着嵌入式系统设计人员在做出决策时多了一个新的解决方案选择,尤其是在把性能、集成度和灵活性视为关键设计考虑因素时,该解决方案更是明智之选。以ARM®处理器为核心的解决方案利用 SoC 方法来降低成本与功耗,增强特性与性能,并将针对低成本、低功耗优化的 28nm FPGA 的优势与具有嵌入式软件开发人员熟悉的业界领先处理器环境,和生态系统的完整平台相结合(如图1 所示)。该新平台将整合赛灵思目标设计平台战略中的许多组件,使软/硬件设计人员能充分利用开放式标准、常见设计方法、开发工具和运行时间平台,从而帮助设计人员减少开发应用基础设施所花费的时间,集中精力为最终产品带来差异化特性。

系统性能为何重要

尽管许多嵌入式系统只需较低的处理能力实现系统控制,不过,大量面向视频监控、汽车驾驶辅助、航空与国防等市场领域的新型应用都要求系统必须集成并处理多个数据集,以便做出复杂的决策,通常是实时的决策。我们发布的新闻稿谈到了有关不同的市场和应用。这些新型应用的共同之处在于,其所需的系统性能水平大大超出了传统处理解决方案能够实现的水平。许多这种应用基本不能用 ASSP 来实现,原先简单用 ASSP 来满足接口、特性和功能要求的情况已经不适用了。

即便性能最高的顺序处理器也难以满足处理多个进入系统的高清数据流数据输入的速度要求。举例来说,智能视频监控将多个分布式视频捕获点整合在一起,对数据进行预处理,并传输至中央主机系统或新一代无线通信系统,而这些系统将判定反馈整合起来,实施高级自适应、预失真及波束形成算法,这种系统突出反映了应用对出色性能水平的要求。

用硬件提升系统性能

处理器系统主导着嵌入式系统市场,同样发挥重要作用的还有由软件开发人员(实际上软件开发人员的数量与硬件工程设计人员数量之比为 10:1)设计并实施成百上千万条高级代码。指令集时延和有限的并行处理能力限制了通用处理器实施高数据强度系统的能力。解决这一难题的常见方法就是采用更多处理引擎同时处理数据。这就要求对代码进行重新分区,实现多核实施,避免重新分区开销抵消性能增益。

另一种传统的嵌入式系统方法就是将 FPGA 用作“协处理器”来分担或加速大量代码或复杂算法的处理工作,从而提高处理器和系统效率。设计人员通过在 FPGA 架构中执行函数,可将函数性能提升 100 倍,这要归功于 FPGA相对于 CPU 的并行处理能力。我们既可采用定制板或模块上的双芯片处理器加FPGA解决方案的组合方式,也可采用内嵌于FPGA本身的处理器来实施。至于多核方法,在 FPGA 中实施软件算法不是没有缺点,考虑到单元成本和实施复杂性等因素,更不用说涉及到开发需要从传统通用处理器中调用软件算法所需的定制处理引擎和API 等因素。对这种系统来说,性能往往受限于不同技术之间的 I/O 接口,特别是涉及到双芯片时更是如此。

许多 DSP 系统都利用采用特定处理参数的专用高性能处理引擎。这种分区方法比较简单,而且比传统的通用顺序处理引擎性能更高,但软件可调用的处理单元数量有限,因此会限制处理能力。

赛灵思可扩展式处理平台将双核 ARM Cortex™-A9 MPCore™ 处理器与关键外设及可编程逻辑完美整合在一起,解决了其他扩展系统性能的解决方案的许多技术局限性问题。处理器和 28 nm芯片可编程逻辑之间的 AMBA® 互联机制确保不会出现降低系统性能的I/O瓶颈。这种新型架构为设计团队带来增值,使其能在 Cortex-A9 处理器和可编程逻辑扩展模块之间进行功能平衡取舍。

过去十年来,整合 SoC 和 FPGA 两大领域并包括可编程逻辑处理器的处理平台稳步发展,这要归功于采用 FPGA 逻辑资源的软处理器内核的发展,以及嵌入 FPGA 内部作为专用资源的硬连线微处理器内核的出现。类似于赛灵思自己的 MicroBlaze® 处理器的软核处理器在可配置性和低成本方面优势明显,但只有先围绕其构建子系统后才能开始开发。目前很多 FPGA 中构建的处理器都没有坚实的子系统,虽然比软核处理器提升了性能,但需要大量配置,然后才能让该处理器系统启动并运行起来。简而言之,上述这两种模式都是以硬件为核心的方法,目前全球很多 FPGA 开发人员都在成功实践。