在“降低静态功耗”的发展历程中,赛灵思采用高介电层金属闸 (HKMG) HPL 工艺仅仅是迈出了第一步,而调整 7 系列器件架构,则又迈出一步。在此前的 FPGA 产品中,赛灵思允许用户采用电源门控技术来关断未使用的收发器、锁相环 (PLL)、数字时钟管理器和 I/O。而在 7 系列 FPGA 中,设计人员可以用同样的方法来禁用未使用的 block RAM 模块。由于block RAM 模块的漏电流占给定器件总漏电流的 30% 之多,因此电源门控技术确实能起到明显的效果。

降低系统总功耗

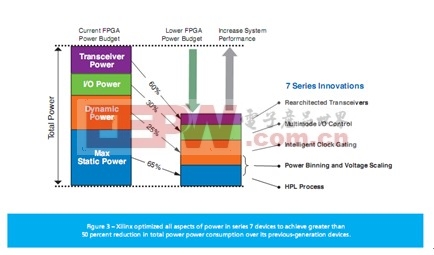

Myron 说,虽然选用高介电层金属闸 (HKMG) HPL 芯片工艺已经显著降低了静态功耗和动态功耗,但赛灵思又进一步采取措施来减少 7 系列器件的系统总功耗,即从由静态漏电流、动态功耗、I/O 功耗和收发器功耗组成的系统总功耗入手(见图 3)。

图 3 – 赛灵思通过优化 7 系列器件的各项功耗,使其相对前代器件而言,总功耗降低一半以上

图中文字:

总功耗

目前 FPGA 功耗预算

较低的 FPGA 功耗预算

提高系统性能

收发器功耗

I/O 功耗

动态功耗

最大静态功耗

7 系列创新

重新架构的收发器

多模 I/O 控制

智能时钟门控

功率分级和电压调节

HPL 工艺