背景

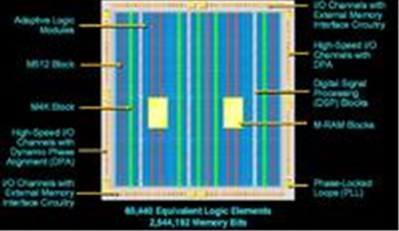

目前以硬件描述语言(Verilog 或 VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至 FPGA 上进行测试,是现代 IC 设计验证的技术主流。这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块。

系统设计师可以根据需要通过可编辑的连接把FPGA内部的逻辑块连接起来,就好像一个电路试验板被放在了一个芯片里。一个出厂后的成品FPGA的逻辑块和连接可以按照设计者而改变,所以FPGA可以完成所需要的逻辑功能。

FPGA一般来说比ASIC(专用集成芯片)的速度要慢,无法完成复杂的设计,而且消耗更多的电能。但是他们也有很多的优点比如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价。厂商也可能会提供便宜的但是编辑能力差的FPGA。因为这些芯片有比较差的可编辑能力,所以这些设计的开发是在普通的FPGA上完成的,然后将设计转移到一个类似于ASIC的芯片上。另外一种方法是用CPLD(复杂可编程逻辑器件备)。

CPLD与FPGA的关系

早在1980年代中期,FPGA已经在PLD设备中扎根。CPLD和FPGA包括了一些相对大数量的可编辑逻辑单元。CPLD逻辑门的密度在几千到几万个逻辑单元之间,而FPGA通常是在几万到几百万。

CPLD和FPGA的主要区别是他们的系统结构。CPLD是一个有点限制性的结构。这个结构由一个或者多个可编辑的结果之和的逻辑组列和一些相对少量的锁定的寄存器。这样的结果是缺乏编辑灵活性,但是却有可以预计的延迟时间和逻辑单元对连接单元高比率的优点。而FPGA却是有很多的连接单元,这样虽然让它可以更加灵活的编辑,但是结构却复杂的多。

CPLD和FPGA另外一个区别是大多数的FPGA含有高层次的内置模块(比如加法器和乘法器)和内置的记忆体。因此一个有关的重要区别是很多新的FPGA支持完全的或者部分的系统内重新配置。允许他们的设计随着系统升级或者动态重新配置而改变。一些FPGA可以让设备的一部分重新编辑而其他部分继续正常运行。

基本特点

1)采用FPGA设计ASIC电路(专用集成电路),用户不需要投片生产,就能得到合用的芯片。

2)FPGA可做其它全定制或半定制ASIC电路的中试样片。

3)FPGA内部有丰富的触发器和I/O引脚。

4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。

5) FPGA采用高速CMOS工艺,功耗低,可以与CMOS、TTL电平兼容。