复数乘法的定义是,两复数相乘,二者各有一个实值和一个虚值。

(a_R + j a_I, where j*j = -1):

(a_R + j a_I) * (b_R + j b_I) =

(a_R * b_R - a_I * b_I) + j (a_I * b_R + a_

R * b_I)

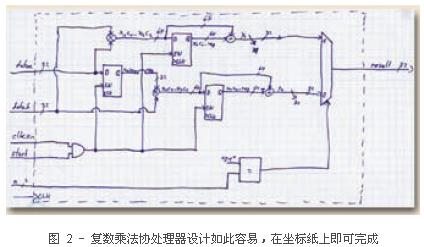

为提高效率,复数乘法硬件模块(cmplxmul) 分三级执行乘法运算。这样,便可在这种多周期的实现中仅使用两个乘法器和两个加法器,从而节省硬件资源。图2所示为复数乘法FCM的框图(草图形式)。

如cmplxmul.vhd中的VHDL代码所示,我们在三个时钟周期中完成复数乘法运算。我们在文件cmplxmul.vhd中实现了用来完成此复数乘法运算的FCM。文件fcmcmul.vhd提供了FCM/APU接口的封装,用来将FCM连接到APU。如我们将在分步指南(请见侧条)中所示,当使用UDI法时,您可以用此封装用作为模板,将自己的FCM连接到APU(“加载存储指令”法需要不同的互连方式)。

我们用Xilinx EDK/XPS 10.1.02通过使用Xilinx ISE® 10.1.02来综合了我们的设计。我们用ModelSim 6.3d SE对设计进行了仿真和测试。

通过增加专用于硬件加速和协处理的用户定义指令,Xilinx Virtex-5 FXT器件中所含PowerPC处理器的APU让嵌入式软件工程师能够以非常高效的方式加速其系统。以本文所述示例设计为起点,您就会发现掌控 APU 易如反掌,让您无需使用专用工具就能大大提高自家设计的性能。