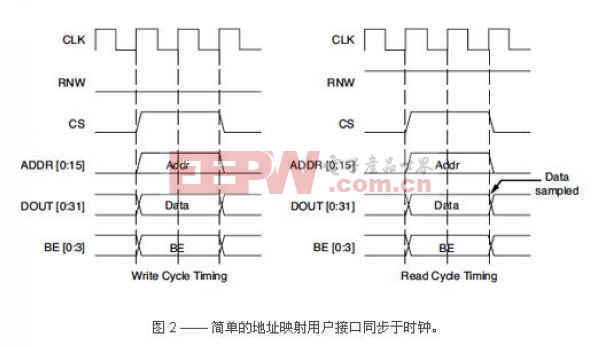

用于可对16位宽的软件映射地址总线进行解码,以将不同的定制接口或外设连接至微控制器。在插入片选 (Chip Select) 两个时钟周期后对读取数据进行采样。

一些预配置的版本可提供串行16450 UART选项。波特率在软件中进行编程,以保持UART独立于时钟输入。调试选择可使用内部FPGA资源,并直接连接至FPGA JTAG接口,从而通过常规FPGA下载线缆实现应用调试。

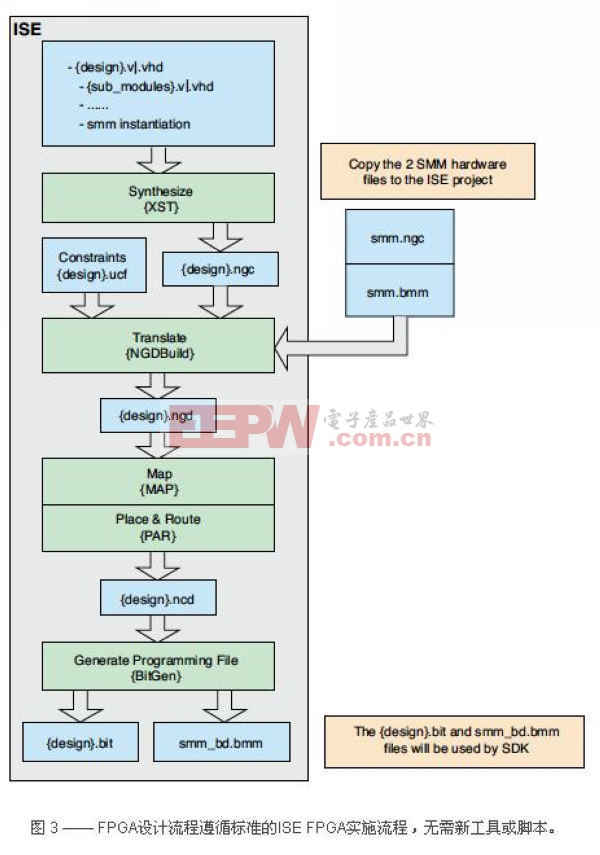

FPGA设计流程

FPGA设计流程遵循如图3所示的标准ISE FPGA实施流程。您可在FPGA设计中的任何层级级别上通过Verilog或VHDL创建微控制器实例。

使用两个与硬件相关的文件 —— 微控制器网表 (smm.ngc) 和Block RAM存储器映射文件 (smm.bmm) —— 即能完成FPGA的实施,用户既不必费心学习新的工具,也不用使用复杂的脚本流程。FPGA嵌入式设计从未如此的简单易行。微控制器配置之间的切换非常简单,只需替换所需的网表文件,然后重新实施FPGA即可。

运行实施工具后, 将额外生成一个文件,指示微控制器所使用 (smm_bd.bmm) 的Block RAM的物理位置。