Synplify把时间戳写入到EDIF,它可用于确定每一个编辑点自上一次的布局和布线运行后是否发生改变。一份tcl文件也由Synplify 写入,从而为赛灵思布局和布线定义分区。当用户指定“syn_hier=locked,physical”时, Synplify把额外属性写入 EDIF之中,要观察的内容包括该模块最近被综合时的时间戳。如果从上一次运行开始模块一直没有发生变化,旧的时间戳被存入EDIF之中。每个标有“locked, physical”的编辑点将含有这样一个时间戳。赛灵思ISE 9.1i 拾取该时间戳,与以前的布局和布线时间戳进行比较,并且只在发生改变的模块上进行增量布局和布线。

总结和优点

一般说来,保存一项设计要比重新实现一项设计更快。因此,如果大部分设计能通过采用Partitions或SmartGuide进行保存,实现这项设计所需的时间将会更少。在用于测试这些技术的广泛的工具套件中平均运行时间的改善,比最初的实现要快 2.5倍。例如,如果一项设计要花3个小时实现,那么,利用设计保存的实现所需时间就要少1个小时。在一些最佳的情形下,运行时间比最初实现要快到6倍之多。

设计保存的另一个优点是减少了验证。如果一个设计模块被严格地保存,那么,那部分设计在设计修改后就不需要再重新验证。因为已保存的实现与前一次的实现是完全相同的,布局、布线和时序是相同的,这样重新验证就没有必要了。

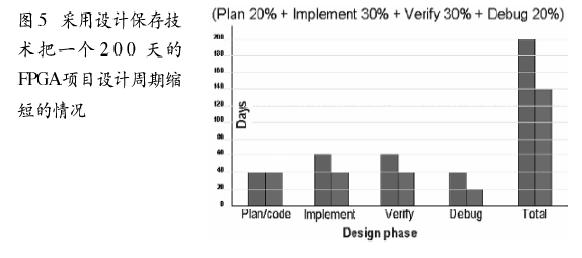

要花大约200天来实现的FPGA设计通常涉及设计定义、实现、验证和调试。分配到每个阶段的预计时间如图5所示。采用设计保存技术,就有可能使解决问题所花费的时间减少几个月。这是基于这样的假定:FPGA 的实现时间是几个小时,因此,运行时间可能被减少。它还假定该设计采用基于模块的验证测试基准,因此,在该设计内已保存的模块不需要被重新验证。如果一项设计采用了这种技术,采用SmartCompile技术获得解决方案所花费的时间就被大幅缩短。