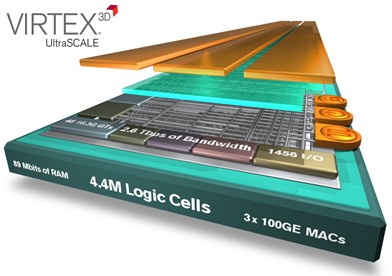

All Programmable FPGA、SoC和3D IC的全球领先企业赛灵思公司 (Xilinx, Inc. (NASDAQ:XLNX) )日前发布拥有440万个逻辑单元的创纪录产品,其密度是业界最高密度产品Virtex® -7 2000T的两倍以上,该器件使其成功在高端器件市场连续两代保持领先优势,并为客户提供了超越工艺节点的价值优势。作为赛灵思推出的All Programmable UltraScale™ 系列的最高端器件,Virtex® UltraScale VU440 3D IC将赛灵思的领先优势从28nm的2倍提升到20nm的4倍,其容量超出任何其他可编程器件。VU440采用先进的3D IC技术,在20nm工艺节点上的容量已经超出了此前公开发布的所有竞争性14/16nm工艺计划。

Virtex UltraScale VU440为新一代生产和原型设计应用提供了5000万个ASIC等效门,树立了全新的行业标杆。20nm Virtex UltraScale器件还为400G MuxSAR、400G转发器和400G MAC-to Interlaken 桥接器应用的单芯片实现方案提供了最高系统性能和带宽。

新思科技公司(Synopsys)IP和系统市场营销副总裁John Koeter指出:“新思科技全面集成的软/硬件HAPS® FPGA原型设计系统已經采用了赛灵思6代器件。我们期待赛灵思Virtex UltraScale VU440功能与HAPS独特的系统功能相结合,将提升整体系统性能和容量,进而为早期软件开发、软/硬件集成以及SoC系统验证等提供更高的生产力。”

Virtex UltraScale系列新增了可重编程功能,为客户带来了全新高度的性能、系统集成度和带宽,而且ASIC级的架构让Virtex UltraScale VU440的可扩展性成为可能,支持新一代布线方案,提供类似于ASIC的时钟和电源管理功能,消除互联瓶颈并能确保关键路径的最佳化,从而能实现高达90%的利用率。除了关键架构模块(如更宽的乘法器、高速存储器级联、33G功能收发器、新增业界领先的集成式100Gbps以太网MAC和150Gb/s Interlaken IP核)的重大进步之外,上述器件还能利用全线速率下的智能处理功能实现数百Gb/s级系统性能。

ARM公司硬件加速技术总监Spencer Saunders指出:“ARM 已经用了以前好几代Virtex FPGA为我们的IP进行验证。 UltraScale架构创新与Vivado相结合,可实现比以往更高的利用率和性能。Virtex UltraScale提供了巨大逻辑门容量、出色的串行带宽以及优异的输入输出引脚,是我们快速开发新一代IP产品的理想选择。”

第二代堆叠硅片互联(SSI)技术对Virtex UltraScale VU440实现业界最高带宽和容量起着重要作用。第二代SSI技术建立在台积公司(TSMC) CoWoS制造技术之上,将芯片间带宽提高了5倍,在整个切片边界采用统一时钟架构,能为设计人员提供虚拟单芯片的设计体验。利用其SSI技术,赛灵思能够提供比其他竞争产品大2到4倍的业界最大容量器件,并持续超越摩尔定律的发展速度。赛灵思于2011年在其Virtex-7 2000T器件中首次采用SSI技术,该产品也是当时全球容量最大的器件,共采用68亿个晶体管,为客户提供了前所未有的200万个逻辑单元(即2000万个ASIC等效门)。

赛灵思的UltraScale器件采用业界独一无二的ASIC级可编程架构,具有ASIC级的优势,能从20nm平面扩展到16nm FinFET技术,以及从单芯片扩展到3D IC。通过结合采用台积公司的尖端技术、协同优化的Vivado® ASIC增强型设计套件以及近期推出的UltraFast™设计方法,赛灵思可实现的系统级性能和集成度是同类竞争产品的1.5倍乃至2倍,达到超越竞争市场一到两年的领先一代优势。