通常FPGA工程师编译较大的工程时比较头疼,因为编译时间非常长,常常需要花费几个小时,如果是在调试阶段,每次修改一个错误需要几小时,这样效率就非常低。导致编译时间较长的原因有两点:1. 设计中资源利用比较大,synthesis、translate和map需要的时间较长;2. 设计的时序比较紧张,需要反复PR来达到最佳时序状态。

如果不想修改工程代码,想要缩短编译时间,则可以采用增量编译技术,其基本原理就是根据前一次编译的结果,只重新编译部分修改过设计,其它部分则沿用前一次编译的结果,这样就可以缩短总体的编译时间。Xilinx的增量编译技术有两种:SmartGuide和Partition。

SmartGuide:这个ISE中的全局优化选项,使能这个选项,编译器在Implementation时会比较前一次编译的Implementation结果,未修改部分则沿用前一次的结果,但是如果时序比较紧张,会根据情况重新实现相应未修改部分来达到时序要求。SmartGuide主要能缩短MAP和PAR的时间。

SmartGuide具体的使用方法如下:

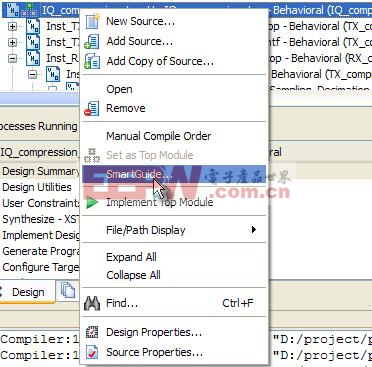

1. 右击top module,然后点击SmartGuide选项。

图1

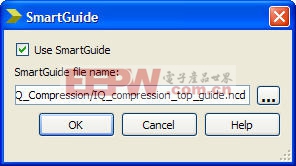

2. 选择前一次的编译信息,其中NCD文件包含当前设计的物理映射信息。

图2

3. 点击OK,使能SmartGuide。

Partition:基于partition(分区)的设计,如果一个partition的HDL代码、时序、物理约束和实现选项未修改,实现工具会采用“复制粘贴”操作保留这部分partition的信息,从而缩短了实现的时间。partition设置后能缩短综合、实现的时间。

自ISE12.1版本后,ISE软件就不再支持partition选项,但是在PlanAhead软件中支持partition功能(ISE快退出Xilinx软件舞台了,据说以后有个Rodin的软件,界面与现在的PlanAhead类似)。如图3所示,在Netlist窗口中右击需要分区的module,然后选择Set Partition即可。

图3

参考文献:

XAPP918:Incremental Design Reuse with Partitions

注: