在28nm工艺节点,赛灵思(Xilinx)给了我们很多惊喜!

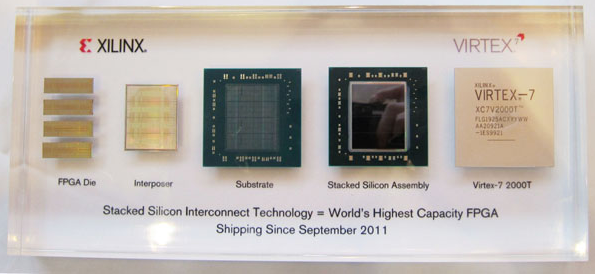

2010年10月,赛灵思(Xilinx)联合台积电蒋尚以发布FPGA 3D封装技术-----堆叠硅片互联(SSI)技术。

差不多一年过去了,在10月26日赛灵思(Xilinx)又给了我们一个大惊喜,发布又一个里程牌式的产品----基于堆叠硅片互联(SSI)技术的世界最大容量FPGA Virtex-7 2000T。Virtex-7 2000T利用68 亿个晶体管为客户提供了200 万个逻辑单元,相当于 2,000 万个 ASIC 门,专门针对系统集成、ASIC 替代以及 ASIC 原型和模拟仿真的市场需求。堆叠硅片互联(SSI) 技术的应用成就了赛灵思(Xilinx)大容量FPGA,而2.5D IC堆叠技术的率先应用, 使得赛灵思(Xilinx)能够为客户提供两倍于同类竞争产品的容量并超越摩尔定律的发展速度。而这是单硅片FPGA在 28nm工艺节点所根本无法实现的。

赛灵思(Xilinx)亚太区销售及市场总监张宇清,全球高级副总裁、亚太区执行总裁汤立人,产品市场营销总监Brent Przybus

本次发布会上,赛灵思(Xilinx)称其堆叠硅片互联技术为2.5D而不是3D。

赛灵思公司全球高级副总裁、亚太区执行总裁汤立人解释了原因,3D堆叠是使用TSV技术将多颗主动元件垂直堆叠在一起, 即主动和主动堆叠,这样的实现方式存在几个挑战,第一是主动元件的散热问题;第二是在高温状态下, 硅通孔(TSV)所产生的应力影响到周边晶体管的性能 (即周边和其它晶体管有快又慢, 不均衡, 影响整体性能)。这些挑战对于很多芯片供应商和晶圆厂来说,在未来2-3年内都没有可行的解决方案。

汤立人接着介绍,赛灵思(Xilinx)的堆叠硅片互联技术是将4个28nm FPGA,通过硅中介层连接。硅中介层是被动的。因为是被动的,中间没有晶体管,不存在TSV应力以及散热问题。赛灵思称其为2.5D技术,认为是可以代替3D的技术。

汤立人认为:“2.5D是一个非常大的转折点。Virtex-72000TFPGA可以加速替代ASIC和ASSP。”据悉,赛灵思是全球第一家部署2.5D堆叠硅片互联技术的企业。而且在FPGA行业,赛灵思(Xilinx)可能是唯一一家适合2.5D技术的企业,这要得益于赛灵思 的FPGA的独特架构。赛灵思亚太区销售及市场总监张宇清解释到:“CPU厂商很难做到,别的FPGA厂商也很难做,因为2.5D技术跟原来的架构非常有关系,赛灵思的FPGA架构是Column Base,加减模块比较方便,每个Column之间是可以连接在一起,四个之间连接起来,走线是最短的。如果不是这种架构,逻辑是随便放的,很难做到。”

Virtex-7 2000T对于拓展FPGA业务发展是非常重要的,体现在:一,可以替代ASIC和ASSP,替代2000万门的ASIC产品。ASIC NRE费用非常贵,想做28nm的ASIC,需要投入5000万-6000万美金,比40nm ASIC投资增加了40%。二,集成度,Virtex-7 2000T在集成度方面非常成功,在功耗,性能,成本方面具有非常优异的性价比。Virtex-7 2000T FPGA可实现180000MIPS,而总功耗控制在20瓦以内。

在总体投入成本相当的情况下,Virtex-7 2000T可把开发时间提高2/3;同时创建集成系统,提高系统带宽,并因为避免了I / O互连而大幅降低功耗。此外还可以加速先进ASIC系统的原型设计和模拟仿真。

Virtex-7 2000T已经开始供货,已经有日本的一家厂商用来做裸眼3D TV。

据悉,赛灵思同时也在进行3D技术的研发,2.5D技术会不会是一个过渡呢?汤立人表示,2.5D会一直走下去的,2.5D有自己的应用,不一定会被3D代替。目前2.5D上所有晶片都是同构的,将来2.5D可以做到异构。也许可以把 65nm的A/D、20nm的存储器,还有CPU等放在一起,实现异构IC互联,那将会带来更多的革新。而且赛灵思明年将会推出基于2.5D堆叠硅片互联技术的7系列HT产品。