Robert Roe最近在Scientific Computing World网站上发表了一篇题为《OpenCL是否会为FPGAs开启大门?》的文章,这篇文章关注了FPGA各种各样不同的应用。他的文章包含了很多领域而不是仅仅局限于OpenCL。如果你对FPGA的印象还停留在20世纪,也就是说FPGA更适合来实现胶连逻辑,那么这篇文中的一些引用确实会让你有所思考。以下就是来自于这篇文中的一些引述:

“FPGA刚出现的时候,它只能做一些非常基本的逻辑比如说布尔代数,那时它确实只是用来实现胶连逻辑的。但是在过去的这些年里,FPGA已经进步和进化了,它拥有了更多专用化的硬化结构。”

“在过去的这些年里,FPGA已经从实现胶连逻辑转变为实现更加复杂的设计,比如说做了很多数字信号处理运算的radio head系统,高性能的视觉应用平台,无线电,医疗装备以及雷达系统。所以它们被用在高性能的计算中,一般用于特定算法的运算。”

“人们选择用FPGA来做这些应用的理由很简单,与利用软件代码实现这些应用相比,FPGA具有更低的单位功耗。”

—— Larry Getman,Xilinx战略市场营销计划部副总裁

有这样一个让人纠结的问题。FPGA具有优越的性能和良好的功耗,但怎么样让那些不精通VHDL或者Verilog语言的开发者,更容易的享受到这些好处呢?

由定义可知,这些HDL(硬件描述语言)是用于描述硬件系统的语言,但系统描述不应限制于HDL这个词,这恰好是目前流行的系统级描述语法。上世纪九十年代之前,电路图作为一种描述语法可以被选择。但是当数字系统变得过于复杂时,就不能用电路图来描述,即使是分层次的电路图也不行。同时,由于HDL编译器变得越来越优秀,因此HDL开始被设计界接受并且保持了长达25年的统治地位。那是一个又好又长的过程,让我们几乎忘记了电路图这种设计方法——一种在被HDL代替之前已经持续了差不多100年的设计方法。这一切都在缓慢地变化。

巧合的是,EEJournal的Kevin Morris最近发表了一篇题为《HLS是新的黑马》的文章。在这篇文章中,Kevin写道:“今天,你可以用C,C++,或者SystemC之类的语言写一些行为性的代码,然后把他们放在HLS工具中,然后迅速返回得到一个详细的硬件设计,这个设计确实要比你自己花费好几个月时间用RTL级描述法做出的设计好的多。这种方法的产出率是惊人的。一个优秀的硬件工程师如果使用HLS连续设计硬件,这跟一个没有使用HLS的工程师相比,他的工作速度要提高5到10倍。同时,当一个使用了HLS的工程师想去做结构上修改的时候,他的工作量和做RTL级修改相比,是非常小的。”Morris几乎可以很容易在25年前写一篇关于HDLs的文章,一个HLS很接近的词。

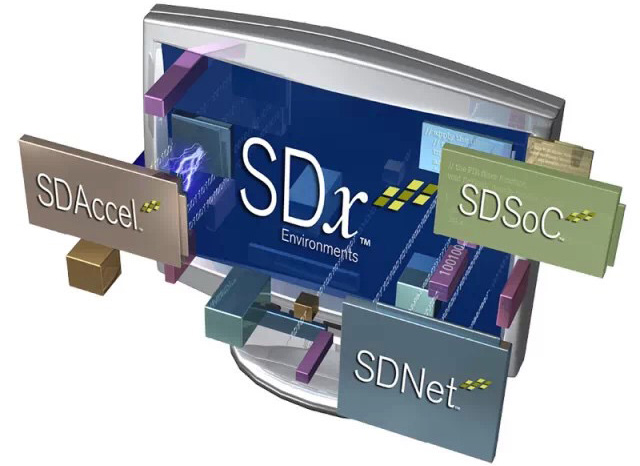

Xilinx最近发布了三个工具,统称为SDx,目的是让系统开发团队使用除了Verilog和VHDL的其他描述语法和语言,来开发复杂的数字系统。Xilinx 的SDAccel 开发环境提供了类似GPU的工作环境,认可OpenCL,C和C++语言写的代码。这是专门为那些喜欢便利的GPU编程和追求速度,但是却又不想在享用高性能的GPUs时,伴随着高功耗的开发者而设计的。SDAccel应用于数据中心加速时,可以让你系统的性能/功耗比提升25 倍。

在Scientific Computing World文章中,Getman写道:“我们的目标就是让FPGA像GPU一样容易编程。以OpenCL为基础的SDAccel,允许开发者使用OpenCL,C或者C++进行编程,而且他们可以以一个很高的层次来开发FPGA了。”

Xilinx发布的最新SDx是集成与SDSoC开发环境,SDSoC是业界第一个C/C++全系统优化编译器。这是一个更加通用的开发平台,提供系统级分析,可编程逻辑自动SW加速,系统连接自动生成,加速编程库以及一个提供给客户和第三方开发平台开发者的设计流程。

SDx的第三个成员是更加专业化的SDNet。SDNet允许创建”软“定义网络,这项技术远超今天的软件定义网络(SDN)架构。软定义网络支持SDN功能,同时也允许软件可编程数据平台硬件的差异,这种软件可编程硬件平台具有在处理包括性能,灵活性和基于内容的网络安全挑战方面能和控制平台软件动态地合作的内容智能。在与应用优化库连接使用中SDNet系统描述是高等级规范的。SDNet将这些规范转化成一个基于Xilinx全可编程器件的优化硬件实现。由此产生的设计实现了在最优成本,功耗和性能方面的线速处理。

SDNet也是复杂数字系统不需要从Verilog或者VHDL开始的另一有力证据。

现在如果你是硬件描述语言的发烧友,祝贺你,Verilog和VHDL将不会很快退出去。Xilinx 的 Vivado 设计套件提供了工业级的硬件描述语言编译器,随着每一个新的软件版本的推出而变得更加地强大,尤其是在配合推出了Xilinx UltraScale 和UltraScale+器件时。SDx开发环境的设计不是取代硬件描述语言,而是补充它们。他们提供快捷和简化的方式让系统跑起来,让它们更快地走出实验室。请确信一点:在此之下的本质仍是真正的硬件描述语言。

原文链接:http://forums.xilinx.com/t5/Xcell-Daily-Blog/Where-do-FPGAs-fit-and-what...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处