在先前的博客中我们研究过I/O约束,下一个合乎逻辑的步骤就是研究如何在我们的设计中用FPGA进行放置和布线约束。使用放置约束的原因如下:为了帮助实现时序,或者为了在设计中提供块与块之间的隔离。在深入开展这个话题之前,有一些术语需要我们定义:

•BEL——逻辑中允许网表元素放置在一个片中的基本元素。

•LOC——在设备中放置网表元素的特定位置

•PBlock——物理模块——用来把逻辑模块限制到FPGA中的某一个区域去。

LOC允许你在设备中定义出一个片或一个其它位置。BEL约束允许你定位到一个比LOC更细的粒度,并且找出片中要使用的特定触发器。而PBlocks可以用来把逻辑组合到一起,并且当我们想进行局部重新配置的时候,也可以用它们来定义逻辑区。

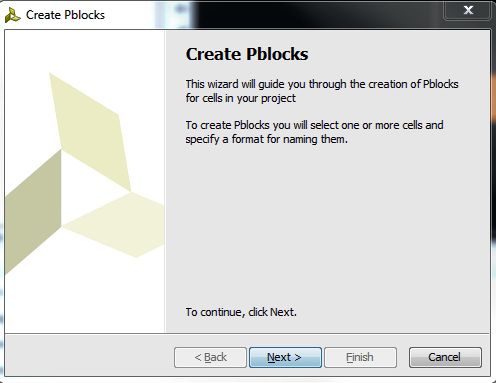

利用Vivado我们可以很轻松的创建使用PBlock。在Vivado中打开一个实现的工程,选择工具菜单->布局规划->创建PBlocks,接着会弹出一个下面的向导来允许你选择PBlock中要包含的叶子节点。

创建PBlock的第一步

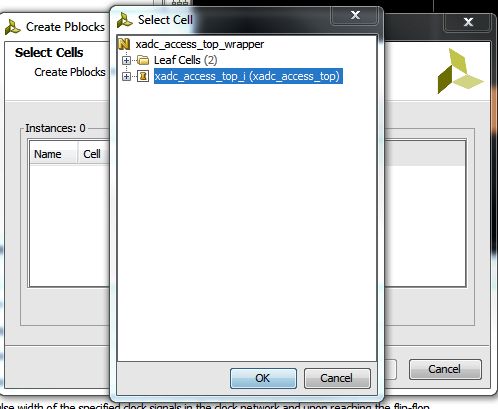

确认PBlock包含的节点

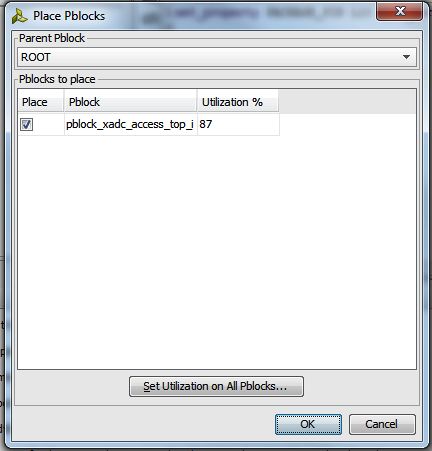

以上这几步将会创建PBlock。但是你还没有规定在设备中的哪个地方放置PBlock。我们可以利用约束文件中的定义或者利用工具菜单->布局规划->放置PBlocks来在设备窗口中描绘出PBlock区域。经过这个步骤过后,在约束文件中会为你自动生成约束。我们也可以利用描绘PBlock选项,在设备中绘制出一个新的PBlock。

把PBlock加载到设计中

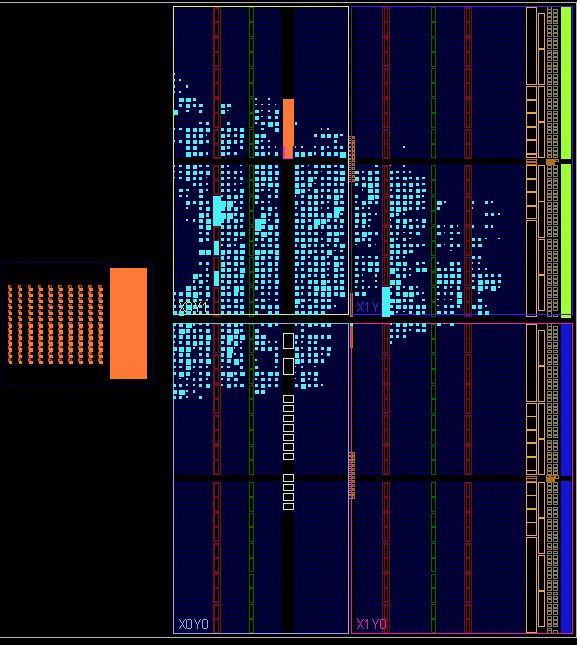

为了演示这个,我打开了一个最近的XADC DMA工程,然后观察没有PBlock时的实现效果,结果如下。此次实现中使用的逻辑区横跨了设备PL边的四个不同区域。如果想把所有的逻辑限制到一个区域中去,我们需要做什么呢?

没有加入PBlock和位置约束的XADC DMA示例

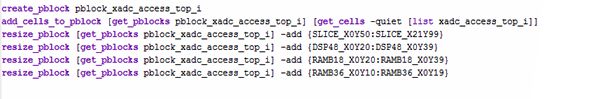

利用PBlock规定设计中所有的逻辑被PBlock包含,再规定块的位置,我们可以实现上面这个目的。在此例中利用上面提到的方法,我将把PBlock限制到包含片、DSP、RAM块的X0Y1区中去。一旦我描绘出PBlock的位置,下面这些将被添加到XDC约束文件中去。

为PBlock增加的XDC约束

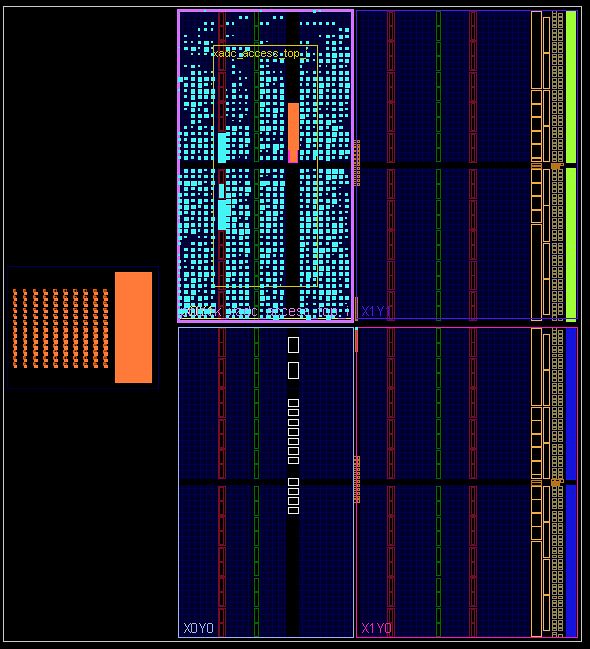

添加新的PBlock后,我重新运行工程,然后得到了下面的布局:

定义了PBLOCK的XADC DMA布局

PBlock很有效,特别是当我们想在设计中分割大块区域的时候,或者我们希望进行局部重新配置。在某些情况下,为了保证最佳时序,你可能想把一些小的逻辑功能综合到一起。当然,我们可以利用PBlock来实现这个,但更常见的是使用相关放置宏。下次我们将研究这个。

原文链接:http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处