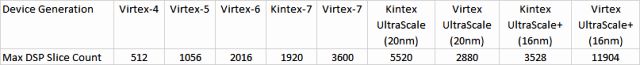

采用16nm工艺的Virtex UltraScale+全可编程器件的最多DSP数量是11904DSP48E2 slices。那是一个很大很大的数目。它已经大到足以让我好好地回顾赛灵思全可编程器件里DSP资源的演化。毕竟11904个DSP slices是一个巨大的数目,但是这个数目与前一代FPGA相比如何呢?回到Virtex-4器件的那段时间,我对网上的数据表和产品表做了一些研究。DSPslices的迅速增加清楚的表明了为什么FPGAs已经几乎接管了DSP的繁重任务。传统的DSP处理器根本没有办法集合赛灵思FPGA的大量并行DSP slices的MACs。

回到Virtex-4代FPGA,下面是赛灵思高端和中档器件的数目:

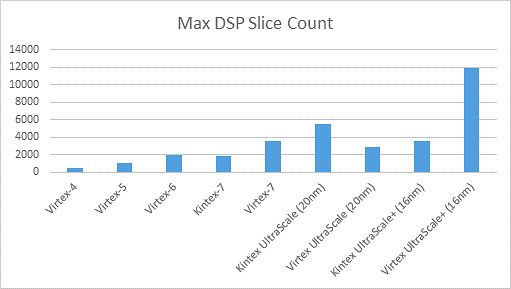

下图是更为直观倾向的数据图表:

注意,Virtex-4一代的器件的生成和制造是采用90nm IC工艺技术,UltraScale+一代采用的是16nm FinFET工艺——两者之间是6代的跨度。当然,这种简单的分析没有考虑DSP48 slices随着时间推移的演变和改进,它仅仅是一个简单的数值计数。

我没有包含赛灵思的低端设备的数据(Spartan-6 和 Artix-7)但是如果你需要大量的DSP ,28nmArtix-7系列的740 DSP slices表现出了相当强大的DSP运算资源相比于最好高端Virtex-4代DSP最大数目提升了近50%性能(由于从90nm到28nm的处理技术的增强,其增加了速度提升,以及扩展的乘法器大大增强了DSP48的设计)。

原文链接:http://forums.xilinx.com/t5/Xcell-Daily-Blog/Evolution-of-a-DSP-monster-...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处