上周的博客中我们学习了Zynq SoC的AXI DMA,我解释了怎样利用AXI DMA控制器将数据从PL搬运到PS。在本期博客中我们将学习怎样完成硬件的搭建。

首先我们要更深入的了解一下AXI streaming接口。Vivado工具的AXI参考手册(用户手册1037)对我们是非常有帮助的,提供了关于Zynq SoC的AXI协议的详细信息,为了构建硬件我们将使用如下AXI协议:

AXI4-Stream—使用DMA时,从Zynq SoC的XDAC流式接口到内存映射,提供高性能输出

AXI4-Lite —配置和控制XADC以及DMA控制器

AXI4 —配置FIFO适配器

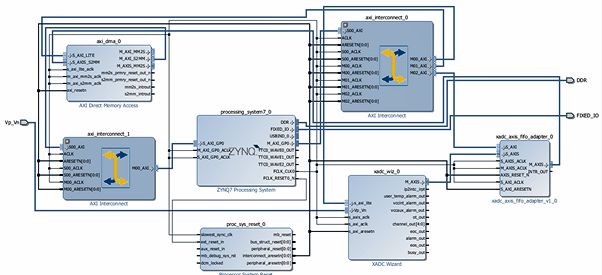

这么多的设置需要使用两个独立的AXI总线:一是PS控制作为主模式,另一个是PS作为从设备。

主模式的AXI interconnect模块允许PS配置和控制XADC以及DMA控制器。这些器件在传送数据前必须进行配置。从模式的AXI端口允许流式的XADC数据,并通过AXI DMA控制器进行数据格式转换,使其符合内存映射交换协议。利用如下端口DMA能够实现双向传输数据:

S/M_AXIS_S2MM —从模式/主模式数据流到内存映射(器件到DMA)

S/M_AXIS_MM2S —从模式/主模式内存映射到数据流(DMA到器件)

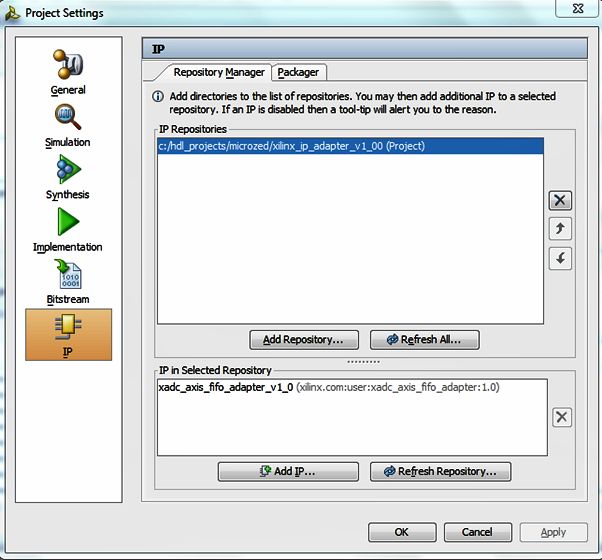

然而与AXI接口实现有一些区别的是,DMA控制器需要使用可选输入端口TLast。XADC与AXI DMA模块不能之间相连,因此需要一个接口适配器来驱动可选输入TLast引脚,这个适配器已经在XAPP1183(使用Zynq-7000 AP SoC处理器系统的XADC AXI接口实现模拟数据采集)的例程代码中提供了。因此可以直接下载例程代码,将这个适配器IP硬核加入到Vivado工具IP核目录中。

将适配器IP核加入到IP核目录中,我们就可以在XADC与DMA端口之间插入这个模块,构建的硬件设计如下图所示:

以此为例,我已经将DMA S2MM主模式输出端口与PS的从模式GP AXI输入端口连接,这样我们就可在片上存储器(OCM)或者片外的DDR SDRAM中存储数据。根据XADC数据传输速率要求,这里采用GP AXI接口是正确的选择。

尽管在这个例程中DMA只以一个方向(S2MM)传输数据,但是如果需要以另一个方向传输数据,MM2S端口随时都可以利用。当然也可以通过自定义IP核移除这些端口并禁止读通道。

在下一期的博客中我们将了解学习软件部分,实现对硬件设计的驱动。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处