By William D. Richard, Associate Professor, Washington University, St. Louis

许多信号处理应用都需要上采样。从概念上来讲,最简单的方法是,对一组向量数据进行M倍上采样可以将该向量数据的离散傅里叶变换(DFT)进行补零处理,插入实际频率分量的(M-1)倍个零后再将补零的向量数据变换回时域。这种方法的计算代价较高,在FPGA中实现时效率也不高。这里提出了一种高效、并行的实时上采样电路,每个ADC时钟生成M个上采样值,其中M是所期望的上采样因子。我们在赛灵思公司的Virtex-6 XC6VLX75T FPGA上实现了一个M为4的上采样,以作为这种通用技术的一个示例。

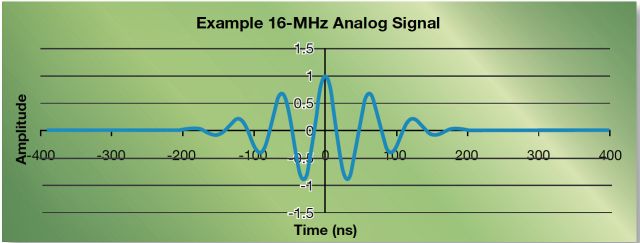

我们的并行上采样技术基于称为“加窗Sinc插值”的概念,有一些优秀文献对其作了详细描述。为便于说明,考虑图1示例子中的16 MHz模拟信号。

图1——用于说明该上采样过程的16-MHz信号示例

该信号可以用下式表示:

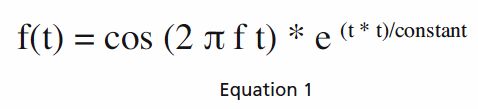

如果对图1所示的信号进行采样/量化,在80Mhz时使用驱动到其满量程输入范围97.7%的一个12位ADC,每个信号周期只采样5次,生成如图2所示的样本数据序列。以因子4对该示例数据序列进行上采样,达到320MHz的有效采样率,可在每一信号周期内提供20个样本。虽然这里描述的方法可以采用更大的上采样因子,但为便于说明,这里的上采样因子M = 4。

图2——这里对图1示例的模拟信号使用80Mhz进行采样,得到了图中的样本数据序列,每个信号周期采样5次,使用12位ADC时可驱动到满量程输入范围的97.7%。

当然,为生成所需的上采样数据向量,简单地在每个ADC产生的真实数据值序列中插入(m-1)个零是可行的(很少被采用)。这种“零插入步骤”在频域中对应的是原始信号频谱的复制。对所产生的“补零”时域信号进行低通滤波,可以消除频域中“重复”的那些期望频谱,可以得到最终的采样数据向量。

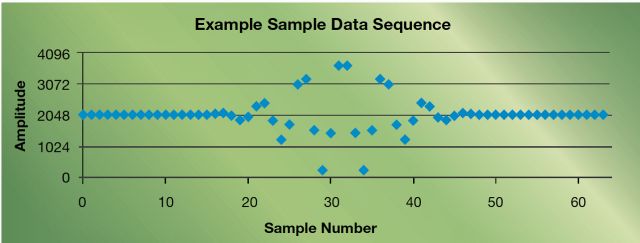

FIR滤波器的设计

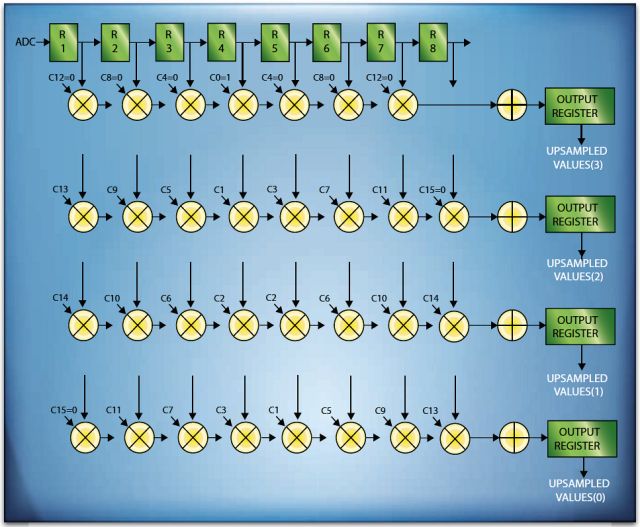

频域中的理想(砖墙)低通滤波器对应于时域中无限扩展的sinc函数的卷积。因此,使补零的时域信号通过运行在m倍ADC时钟速率的一个对称低通FIR滤波器,可以执行所需的近似卷积运算,其拓扑结构如图3所示的31抽头FIR滤波器。通过这种方式,我们可以实时产生上采样数据向量。在图3中,R1,R2,……,R31代表M倍ADC时钟频率的寄存器,而C0,C1,……,C15代表FIR滤波器的系数。

图3——在补零时如果时钟频率为基础ADC时钟速率的M倍,那么可以使用一个31抽头的FIR滤波器在每个时钟周期产生一个上采样数据值。

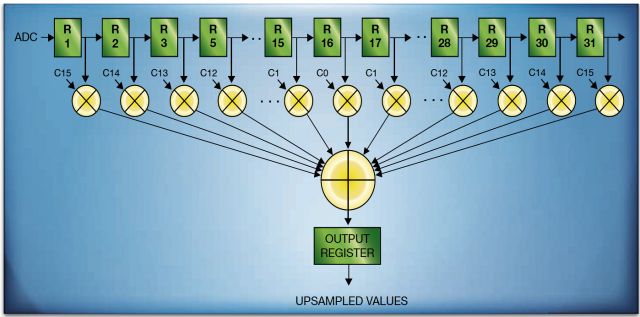

需要注意的是,任何时钟间隔内,图3所示FIR滤波器的寄存器大部分包含的是零,而不是实际采样数据。比如,当M = 4时,R1包含实际采样数据,R2、R3和R4将包含零。R1包含实际样本数据时,R5、R9、R13、R17、R21、R25和R29包含的也是实际采样数据,其余的寄存器则包含零。在下一个时钟间隔,R2、R6、R10、R14、R18、R22、R26和R30将包含实际采样数据。因为每M个采样数据中,有(M–1)个在通过图3所示的FIR滤波器时是零,因此在M = 4的情况下,您可以如图4所示拆叠该31抽头的FIR滤波器,并行产生M个输出。通过这种实现方式,并行FIR滤波器可以以基础ADC时钟速率运行,而不用工作在M倍ADC时钟速率上。

图4——通过观察图3,在任何给定的时钟周期内,每四个寄存器只有一个非零数据,因此可以折叠该滤波器,折叠后该滤波器以基础ADC时钟速率运行,并行生成四个输出。

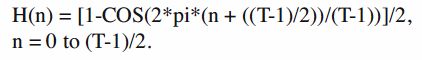

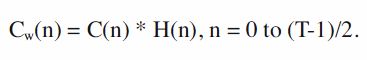

您可以指定窗口sinc函数系数,如图4所示中的Cw(n),以尽量减少实现FIR滤波器时的乘法器数目。对于一个T抽头的低通FIR滤波器,其最佳系数可以用下式表示:

![]()

其中的Hanning加窗系数可以用下式表示:

加窗Sinc函数系数,Cw(n),可以由对应的C(n) 和 H(n)相乘得到,即,

当M = 4时,一个31抽头的FIR滤波器的系数按上述公式计算,C0 = 1.0并且C4 = C8 = C12 = C15 = 0,图4中这些系数相关的9个乘法器将不再需要。此外,为生成UPSAMPLED VALUE(1)每个系数要使用两次,因此您可以“折叠”该实现——比如在乘法之前将R1和R8相加——这将再次减少四个乘法器。为生成图3中的四个上采样值,最终的设计仅需要共计18个乘法器——与之形成对比的是,补零后,您也可以使用一个31抽头的FIR滤波器产生该上采样数据,每且时钟频率是基础ADC时钟速率的M倍。值得注意的是,采用上述技术的滤波器设计,在离开并行滤波器时每个原始采样值并未修改。

注:本文是第89期Xcell daily中一篇文章的缩短节选版本,原文题目是“利用Xilinx FPGA实现高效并行实时上采样”

点击这里下载第89期Xcell期刊的PDF版本

点击这里在线阅读第89期Xcell期刊

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Efficient-Parallel-Real-Tim...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处