作者:Steve Leibson, 赛灵思战略营销与业务规划总监

赛灵思All Programmable 器件低端产品组合中包括三大器件系列,因为大量DSP硬件处理模块都集成进了这三大系列的可编程逻辑架构中,它们都给DSP设计师提供了有趣的选择。这些DSP处理模块---赛灵思官方称谓是slices,都已经集成进乘法器和累加器中,并且已经针对最常用(以及不常用)的DSP进行了优化。

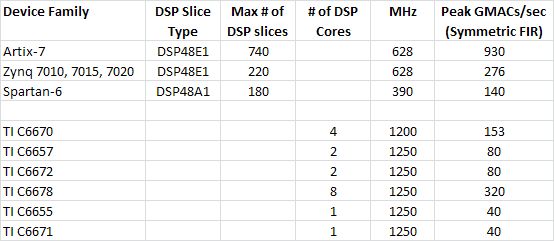

下表显示了在每个赛灵思低端产品系列(Zynq、Artix-7和Spartan-6)中,可以使用的DSP Slices最大数量,以及你可以从这些器件获得GMAC/s(每秒亿次乘法累积操作)峰值。为便于比较,表中还显示了你可以从TI的C66xx多核DSP系列得到的每秒GMAC峰值。

正如你所看到的,赛灵思低端All Programmable器件在较低时钟频率下比传统DSP提供明显更多GMAC/s性能,原因很简单:并行性!在这些低端器件中有大量乘法器和累加器,DSP就是一种GMAC游戏。 (当然,高端的Zynq SoC和赛灵思的Kintex-7、Virtex-7、Kintex UltraScale和Virtex UltraScale All Programmable系列器件则可以提供更高DSP性能。)

除了提供基础的GMAC性能,把这些高性价比低端All Programmable器件用于DSP应用的另外一个优势是实际的能效优势(性能/瓦)例如,TI的TMC320C6678多核DSP功耗大约是12.3W,并提供320 GMAC/s的性能,归一化后就是26 GMAC/s/ W。

而Artix-7 All Programmable器件可以提供140 GMAC/s/W,这可是TI器件的五倍多!

现在,你可能在想,用类似这样低端All Programmable器件的硬件芯片去实现DSP算法会不会太难了?基于硬件可编程器件的DSP设计会不会不适合你现有的设计流程?其实并不是那样的,例如,如果您正在用MATLAB或Simulink开发基于模型的DSP算法,您就已经涉及了赛灵思的System Generator和Mathworks的HDL编码器。如果您目前在用C或C + +写DSP算法,那用赛灵思的Vivado HLS工具也可以干这事。

好玩吧?想了解更多信息吗?请点击这些链接吧

赛灵思官网DSP解决方案

Vivado设计套件用户指南:用System Generator完成基于模型的DSP设计

安富利公司带有高速模拟功能的Kintex-7 FPGA DSP 套件

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处