作者:Steve Leibson, 赛灵思战略营销与业务规划总监

Adam Taylor's博客系列讲解基于ARM的Zynq SoC芯片可编程逻辑实现定点算法以提高性能。

这个博客系列每周发布,迄今为止已经发布了6个月,我们在Zynq SoC处理器系统(PS)中实现了转换函数,并粗略测量了计算时间。在这个博客中我们开始了解在之前创建的外设添加VHDL(或Verilog)代码所需要执行的任务,以实现和加速同一转换函数。我们将使用定点数值系统执行这个任务。因此本篇博客将介绍定点函数,以及如何在Zynq SoC可编辑逻辑中如何实现这个函数。

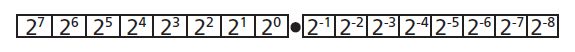

在设计中有两种方法表示数值:定点和浮点。定点表示指小数点在固定位置,极大简化了算术运算。定点数由两个部分组成:整数部分和小数部分,如图所示:

数值的整数部分在隐小数点左侧,而数值的小数部分在隐小数点右侧。上述定点数能够表示在0.0至255.9906375之间的无符号数,或者使用两个补码表示在–128.9906375至127.9906375之间的有符号数。

浮点数由两个部分组成,即指数和尾数。浮点表示法使得小数点按照数值的数量级在数值内浮动。

定点数的缺点是表示较大数值或获取带有小数的精确结果值时,需要更多的位数。虽然FPGA可支持定点数和浮点数,但大多数应用程序选择使用定点数,主要是因为定点数系统更容易实现。

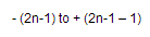

在设计中我们可选择使用符号数或无符号数。一般地,怎样选择数值受所实现的算法约束。无符号数可表示0 至2n – 1之间的数值,总是表示正数。符号数使用两个补码数系统表示正数和负数。两个补码数系统可利用两个数相加来表示一个数减去另一个数。两个补码数可表示为:

在定点数中表示整数位和小数位之间分割的一般方法是 x,y,其中x表示整数位数,而y表示小数位数。例如8,8表示8个整数位,8个小数位,而16,0表示16个整数位,0个小数位。

在许多情况下,在设计时已经确定整数位和小数位的位数,一般按照浮点算法转换。由于FPGA具有灵活性,可表示任意位数的定点数;FPGA支持32位、64位或甚至128位寄存器。FPGA同样支持15位、37位、1024位寄存器。我们可扩展硬件准确地解决问题。

必要的整数位数取决于需要存储数值的最大整数值。小数位数取决于结果值所需的精确度。

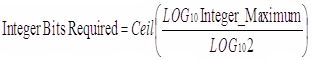

要确定必要的整数位数,需要使用以下等式:

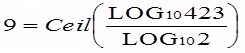

例如必要的整数位数表示0.0和423.0之间数值的等式为:

我们需要9个整数位,表示0至511之间的数值。

必须对齐两个定点运算数的小数点以加、减、乘、除这两个数值。即,x,8数只能与同样在x,8表达式中的一个数加、减、乘、除。执行不同x,y格式内数值的运算,必须首先要对齐小数点。注意严格来说,在除法算式中不需要对齐小数点。但执行定点除法需要仔细考虑以确保结果值能够被除尽,不会出现负数。

同样,将两个定点数相乘时也不需要对齐小数点。按照乘法得出结果值格式为X1 + X2, Y1 + Y2 。也就是说,将两个格式分别为14,2和10,6的定点数相乘所得出的值为24,8(格式为24个整数位和8个小数位)。

如果需要除以不变常数,我们当然可通过计算常数的倒数,将结果值当做乘数以简化设计。通常,使用这个方法可完成更为有效的设计实现。

以上就是有关定点算法的讲解,我们将在下个博客系列中讲述在FPGA内使用定点数系统执行函数。

顺便说下我将在EElive演讲!时间就是本周,地点在加利福尼亚州圣何塞市。如果您也参加活动,遇到我别忘记与我打招呼,我也期待与您见面。以下是我的日程安排。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/The-Zynq-PS-PL-Part-Six-Ada...

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处