作者:Steve Leibson, 赛灵思战略营销与业务规划总监

INVEA-TECH和CESNET(捷克共和国国家研究所和教育网)演示了一个方法,并行使用两个FPGA PCIe Gen 3×8接口来维持从100Gbps以太网端口到CPU主机的数据传输。这个概念叫做分岔(bifurcation),几年前在英特尔Core I7 CPU中被引进。因特尔试图允许将CPU的PCIe的16个端口分开,使得他们可以处理两个独立的任务,当然相反模式下也能工作,比如将两个外部PCIe8端口合并为一个16端口。使用分岔在单个FPGA上建立一个100Gbps的系统,这消除了对额外PCIe切换芯片的需求,可以节省成本、板上空间和大约6W的功率。

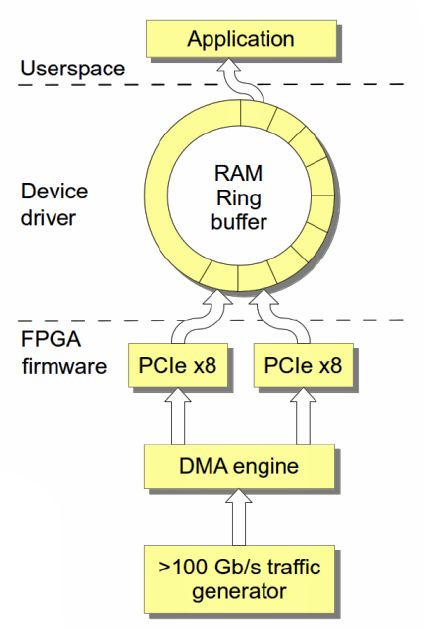

CESNET和INVEA-TECH进行了一系列实验来展示PCIe分岔的好处。测试程序包括装载一块赛灵思Virtex-7 H580T 3D FPGA的FPGA卡。两块FPGA PCIe x8硬块接入卡上的PCIe x16卡槽。运行了Linux设备驱动的FPGA固件将数据传输给位于PC RAM中的环形缓冲区。PCIe x8接口使用round-robin的方式将数据传输给单个缓存。下面的方块图显示了实验过程:

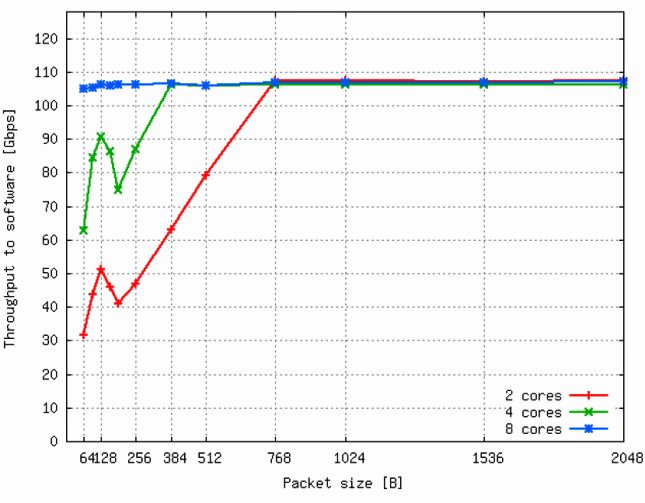

在FPGA生成的超过100Gbps的流量中,例化了随机的分组数据生成器。下图显示了传输速率的结果:

DMA引擎在FPGA组包中例化,因此分组长度不会影响原始PCIe吞吐量。可达到的吞吐量为107Gbps。注意到,至少需要8个CPU核为较小的分组缩放进程,以达到目标的100Gbps。

关于这次实验的更多信息,见INVEA-TECH白皮书。“CESNET and INVEA-TECH demonstrate 100 Gbps transfers over PCIe with a single FPGA.”

关于Xilinx Virtex-7 H580T 3D FPGA的更多信息,这里有个视频,讨论了该器件28Gbps串行收发器,另一个开发100Gbps以太网系统的关键元素。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Need-to-get-100G-Ethernet-d...

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处