作者:Adam Taylor

在我的上一篇博客中我介绍了利用Zynq SoC上的两个ARM Cortex-A9 MPCore处理器执行不同的任务程序,实现非对称的多进程处理模式的概念。我期望你能坐得住因为这篇博客有点长,但是我们会有收获,到最后我们会让我们的AMP系统启动并运行,在我们实现AMP系统启动并运行之前会进行很多步的准备工作,但是这些都非常的简单所以不用担心。

在Zynq SoC上搭建AMP系统的关键是配置好一个启动引导加载程序,第一阶段的加载程序执行完毕后处理器会寻找这个执行文件并加载到内存中。不幸的是我使用的Vivado工具是2014.1版本(因为我最近在搬家没有网络所以不能下载最新的版本),当我们生成FSBL(第一阶段启动加载文件)时这个版本不支持AMP,因此为了能够完成这个例程我将使用赛灵思应用笔记XAPP1079中提供的修改过的FSBL文件和standalone OS文件。(源文件下载链接 http://www.xilinx.com/support/documentation/application_notes/xapp1079-a... )

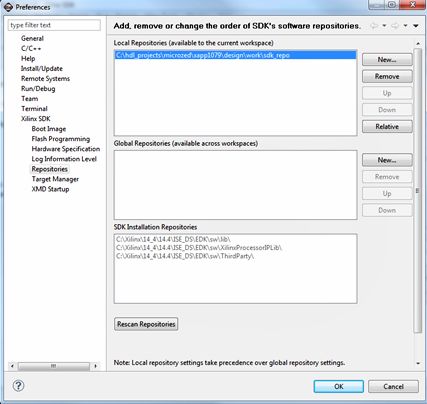

下载好压缩包文件后第一部是将文件解压到你期望的工作目录下,并给文件夹重命名为SRC。这些文件包含了修改过的FSBL和standalone OS文件。我们需要让SDK软件能够找到这些文件,因此下一步是要设置更新一下SDK存储库目录让SDK能够找到这些文件。在SDK软件菜单来点击Xilinx tools,在下拉菜单中选择repositories,创建一个新的存储库文件目录,路径为你的工作目录>\app1079\design\work\sdk_repo,具体如下图所示:

添加好存储库后下一步就是要生成以下文件:

•AMP第一阶段启动引导加载程序

•Core 0 的应用程序

•Core 1 的应用程序

我们要为每个处理器内核生成BSP(板级支持包)文件:

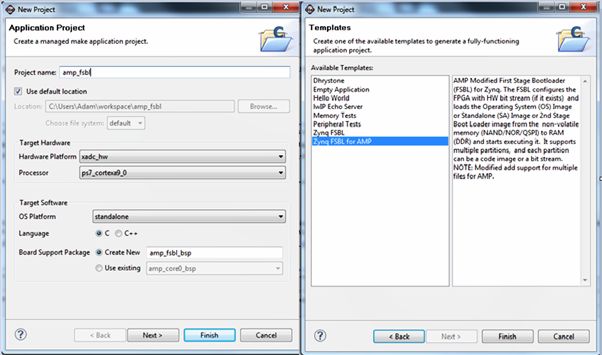

第一步是创建FSBL,选择file -> new application -> project,这样才能够让我们创建一个FSBL工程,实现AMP处理模式,这些步骤和以前没什么区别,但是我们选择Zynq FSBL for AMP 模板,代替以前选择的Zynq FSBL模板.

接下来我们要为第一个处理器内核创建应用程序,这步同样很简单。以前我们已经做过很多次了,这里要确保选择的是Core 0 和standalone OS并且创建自己的BSP文件。

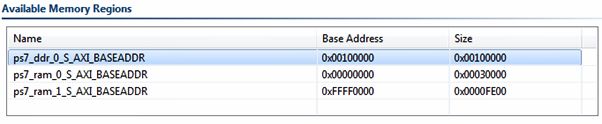

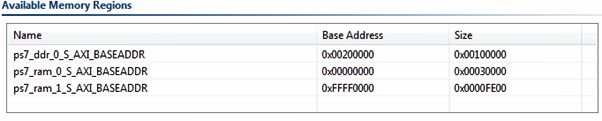

一旦我们为内核创建了应用程序,我们需要正确的定义DDR内存的映射地址,因为程序将从这些地址开始执行。我们需要编辑链接脚本,如下图所示显示除了DDR内存的基地址和大小。这一步很重要,如果我们不能正确的为Core 0和 Core 1定义内存地址和大小,在程序执行的过程中就会产生内核间的冲突,出现段地址错误。

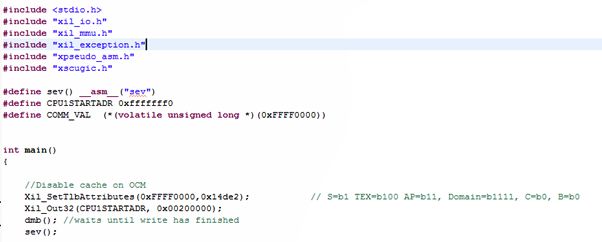

现在我们就可以编写Core 0执行程序的代码了。这部分是AMP 系统的核心,它将从Core 1开始执行程序代码。我们要在应用程序代码中包含以下部分代码。这部分代码禁止了Zynq SoC片上存储的缓存功能,定义了Core 1的起始地址,这个地址是Core 1的内存映射地址范围之内的,具体可以查看先前定义的链接脚本。一旦Core 0 执行Set Event(SEV)命令,就会让Core 1开始执行它负责的程序代码。

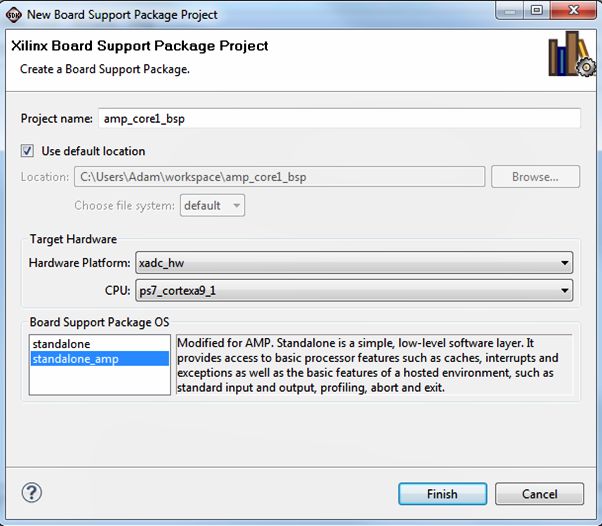

下一步是要为Core 1创建BSP文件,我们将使用修改过的standalone OS模板(standalone_amp),这个模板禁止了PS部分的监听控制单元(SCU)的重复初始化。因此,我们不能允许自动生成BSP文件,这与Core 0的操作是有区别的。还有就是确认在CPU的选择项中选择的是Core 1。

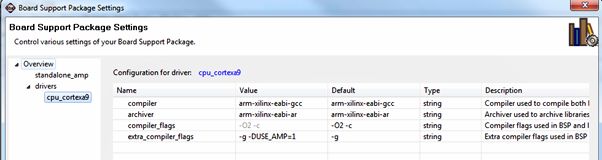

既然我们已经为Core 1创建了BSP文件,但是在我们编写Core 1执行的应用程序代码之前,我们要修改BSP的一些设置,这一步非常简单,需要在驱动配置对话框中增加一个额外的编译标志---–DUSE_AMP=1,具体操作参照下图:

完成以上这些操作后,我们就可以为Core 1创建应用程序。按照下图所示,确保处理器选择的是Core 1,BSP选择的是前面步骤中刚刚建立的amp_core1_bsp。

同样我们还需要定义正确的DDR内存映射地址,这个地址是Core 1程序执行的映射地址,这些映射地址可以通过编辑Core 1的链接脚本文件获得。

在这个应用程序的代码中,我们也要禁止片上存储的缓存功能,因为在后面的博客中,我将介绍使用这部分内存实现两个处理器内核之间的通信。

当我们完成了应用程序,并且编译了整个工程,我们应该拥有以下几个文件:

•AMP FSBL ELF

•Core 0 ELF

•Core 1 ELF

•配置PL硬件部分的比特流(bit)文件

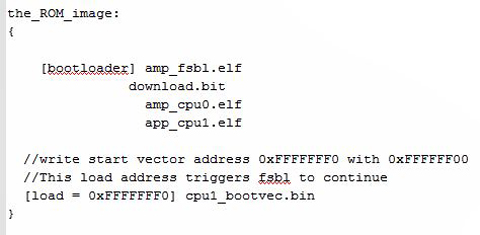

最后我们需要生成.bin格式的文件,可以让Zynq SoC从我们所配置的内存地址启动。我们同样需要一个.bif格式的文件,这个文件中定义了我们生成.bin格式文件的源文件和路径信息,同时也规定了源文件的调用顺序。

在这里我们将不使用SDK软件中创建Zynq 启动镜像的功能,我们将使用ISE命令和.bat批处理文件,这在XAPP 1079的design\work\bootgen目录下已经为我们提供了。这个目录下包含了bif格式的文件和cpu1_bootvec.bin文件,这些文件用来修改控制FSBL文件,防止它寻找并加载更多的应用程序。

在生成bin格式文件之前,我们要将下图中所示的三个ELF格式的文件拷贝到bootgen目录下,编辑BIF格式的文件确保我们使用的elf格式的文件的名字是正确的。

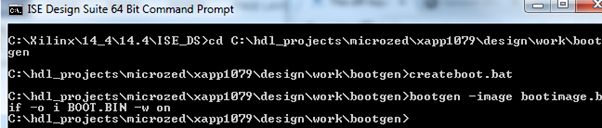

现在我们可以打开ISE Command Prompt,参照下图输入命令进入到bootgen目录,运行createboot.bat批处理脚本,在bootgen目录下就会生成我们所需要的boot.bin文件:

这个文件要被下载到Zynq SoC片上非易失性的存储器件中,启动这个器件将会激活Zynq SoC片上的两个处理器内核,并且执行它们各自的应用程序。

在我的下一篇博客中,我将会更加详细的介绍运行在Zynq SoC上的双核ARM Cortex-A9处理器中的软件应用程序。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处