作者:Steve Leibson, 赛灵思战略营销与业务规划总监

上周在X-fest San Jose大会上,我参加了四个技术座谈会,第一个就是关于存储器接口和FPGA的,尤其是Xilinx的UltraScale系列FPGA。这次座谈会上有很多关于SDRAM的有价值的资料。Bryan Fletcher是Avnet(安富利)的一名技术 营销总监,他的演讲是从分析DDR3与DDR4 SDRAM的动态市场占有率开始的,DDR3 SDRAM目前是市场占有率的主体,也就是说DDR3 SDRAM存储器的每比特成本要比其他SDRAM成本要低,性价比要高。

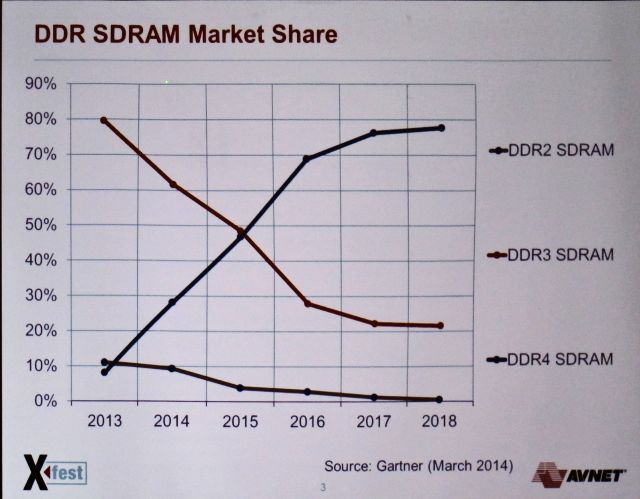

这样的市场格局不会一直持续下去,下面图片显示的是Gartner对于2018年之前的SDRAM市场份额占有形势的预测:

正如你所看到的,曾经的市场主体DDR2将走向没落,它的市场份额占有率将从10%下降到5%。 这意味着将下降到很难再有销量的水平,市场主体DDR3 SDRAM在下一年年初之前它的市场需求将是必不可少的,会呈现一种与DDR4 SDRAM平分秋色的形势,但是之后DDR3的市场占有率将会迅速减少,DDR4 SDRAM将会成为市场的领导者。

原因?为什么?

我们可以从三个“P(单词首字母)”方面分析——价格(price)、性能(performance)、功耗(power)

——这些正是电子电气工程所关心的问题。Fletcher解释说DDR4 SDRAM将会是在这三个方面都是最出色的。正如上面的图表显示,DDR4 SDRAM将会占据大部分的市场份额,主要是靠PC市场销量的推动。市场占有率会推动产品的更新,同时反过来也会影响产品的价格。请注意SDRAM在FPGA市场的销售情况与PC机市场的形势如出一辙。而且DDR4 SDRAM将会使用更先进的处理技术来生产,这意味着每个SDRAM芯片的存储容量将会翻倍,根据Fletcher所说,在不久的将来这两个因素将会使DDR4每比特存储的成本降到最低,这是你开始你的下一个项目设计所需要考虑的一些方面。

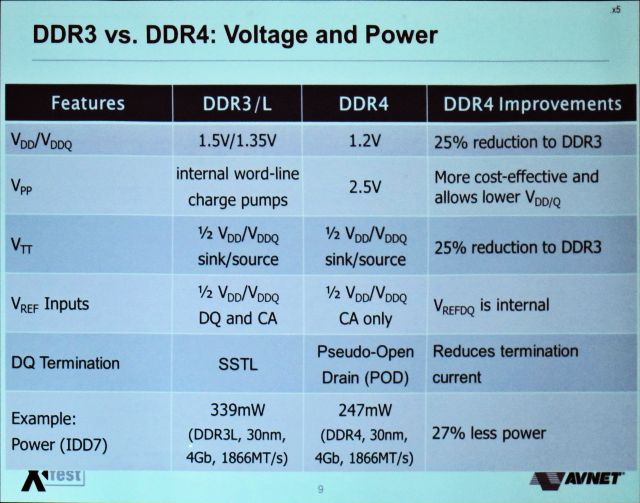

Vdd/Vddg——RAM存储阵列的核心操作电压,比DDR3降低了25%

Vpp——用于内部的充电,DDR4 SDRAM采用外部驱动,这是芯片级的设计变动,允许更低的核心操作电压(1.2v)

Vtt——总线端点电压,是Vdd电压的一半,所以与DDR3相比也降低了25%

这些改进了的低电压设计让DDR4成为低功耗高性能的SDRAM,下面的图表DDR3与DDR4相关信息的对比:

最后就剩下性能没有介绍了,DDR4 SDRAM将来能够达到最快3200Mbits/sec的数据交换速率,而DDR3 SDRAM最快只有2133Mbits/sec。因此没有比较可言(注:Xilinx 基于20nm制作工艺的UltraScale系列FPGA与DDR4之间的数据传输速率能够达到2400Mbits/sec,仍然要比DDR3的传输速率要快)。.

这次讨论会引导我们关注FPGA所使用的SDRAM存储芯片,尤其是Xilinx UltraScale系列的FPGA芯片。

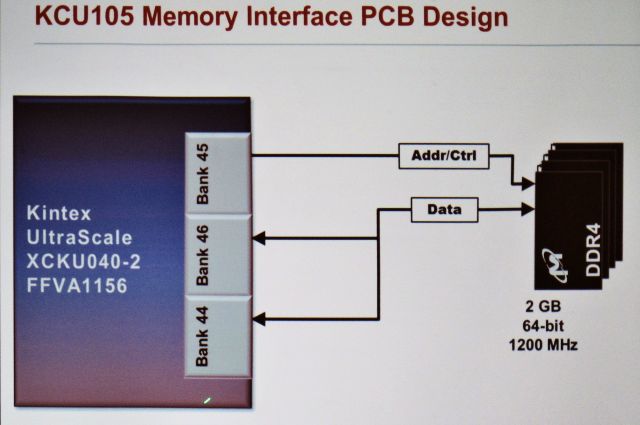

UltraScale系列的每个I/O Bank已经扩展到了52 bits,因此每个Bank能够支持四个全字节的通道,你需要三个Bank来至此64-bit的存储实现,因为它需要八个全字节的通道用于数据传输,还有一条地址和控制信号通道,如下图所示:

此外,在每个Bank的内部还有两个PLL,所以你可以使用一个Bank来控制两个不同的存储Bank,如果有需求的话。

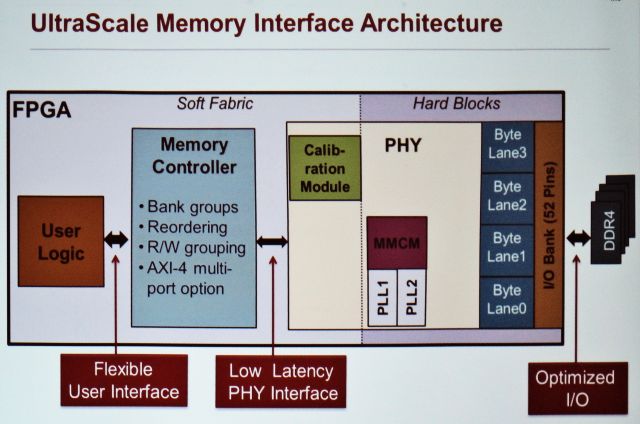

位于UltaScale FPGA内部的存储控制器是由MIG(Memory Interface Generator)工具生成的,与Xilinx以前的FPGA产品是相同的。DDR4 SDRAM的容量信息已经被加入到MIG工具中,存储控制器的具体实现分为硬核模块包括PHY和在PL部分实现的模块,主要包括存储控制器和SDRAM校准模块,如下如所示:

最后,Fletcher强调你需要注意印制电路板的布局布线,这将影响到DDR4的数据传输速率,这里我们给出了一些参考材料(UltraScale Architecture PCB Design User Guide (UG583)),什么也比不上一张图片所能够说明的问题:

AvnetX-fest系列会议正在北美地区举办,可能哪一边就会到你附近的城市,点击这里查看具体信息。

欧洲之行会在十月份启动,点击这里产看日程和城市安排信息。

要了解亚洲的日程安排信息,点击这里。

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处