作者:Adam Taylor

在MicroZed 以往的经典案例中,修改和更新PicoBlaze 的传统方法是使用JTAG下载器。Zynq SoC的处理系统提供额外功能让我们可以建立一个更加灵活的Zynq 程序下载系统以适应更多工作。我们可以使用 Zynq PS(处理器)访问Zynq SoC的PL侧的BRAM存储器,这是存放PicoBlaze 程序的地方。我们通过使用AXI BRAM控制器来实现。我们曾在以前的MicroZed 经典系列的NeoPixel 案例中探讨过BRAM控制器。

这种方法确实需要更多操作步骤,因为我们不能使用PicoBlaze 汇编器生成的存储 VHDL文件。但是,我们将使用标准的IP模块,所以也并不是想像的那么难。相反的,我们首先建立一个双端口RAM并且使用PicoBlaze 汇编器生成的hex文件来初始化它,这样在上电之后PicoBlaze 处理器的内存就有可执行的程序。

我们放在双端口RAM内的程序与PicoBlaze 汇编器生成的VHDL文件没什么不同。尽管程序也可以跑在单端口内存,这多出来的这个端口使ARM Cortex-A9多处理器可以访问这个共享的双端口内存,并且在开发过程中可以覆盖这个内存的内容,如果需要的话。这个技巧可以很容易按照需求改变PicoBlaze处理器的可执行程序。

如果要举个例子,其优点能够重复编写PicoBlaze 处理器的程序,那么就在成像处理中生成一个波形能够驱动一个CCD(电荷耦合装置)。因为这个PicoBlaze 处理器是非常适合生成这个波形。然而,CCD成像设备在程序运行期间经常要求修改波形时序来完成成像性能优化。在运行过程中能够修改波形是非常重要的并且使用软驱的方法也很方便。

在模块图中我们在PicoBlaze 原件上右击并且选择“edit in IP packager”来添加双端口存储器到这个PicoBlaze 处理器中。这将打开一个IP包并允许我们修改我们以前建立的元件。第一件事就是从工程中删除VHDL内存文件,并且建立一个新的双端口存储器,通过使用IP Catalog 添加一个新的模块memory generator。

双端口RAM的A端口和B端口的设置是非常简单,端口A连接到AXI BRAM控制器并且B端口连到PicoBlaze。RAM的配置如下:

•接口类型:native

•选择真双端口RAM

•端口A选项:

•写宽度32

•读宽度32

•使用32bit地址(由于AXI BRAM控制器要求)

•操作模式:写优先

•使能端口类型:使用ENA

•使用32bit地址

•端口B选项:

•写宽度18

•读宽度18

•操作模式:读优先

•使能端口类型:使用ENA

•原语输出寄存器不能预置

由于我们希望使用初始化文件来预先配置BRAM,所以我们需要一个coe文件,我们特地将“other options”勾上。我们使用PicoBlaze 汇编器生成的HEX文件,你只需要在这个文件的顶部做些如下修改:

memory_initialization_radix=16;

memory_initialization_vector=

然后你可以将该文件添加到PicoBlaze 处理器的内存,在上电之后可以被PicoBlaze 执行。

我们使用32bit地址,以致我们能够确保从PicoBlaze 到BRAM存储器访问是正确对齐的。那么,我们需要确保32bit存储器的最低两个地址没有被使用,那样就可以自动使字对齐。

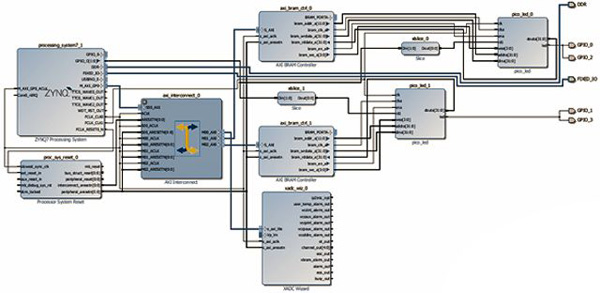

现在,我们可以在PicoBlaze 元件顶层连接双端口RAM,并且重新封装这个IP,使我们模块图中例化的PicoBlaze 能够得到更新(使用Tools -> Report ->Report IP Status,查看IP是否自动更新)更新完IP后,我们能够添加AXI BRAM控制器并且连接到 Zynq SoC处理器的AXI总线。做这一步可以让我们的ARM Cortex-A9 多核处理器也能读/写连接到PicoBlaze 处理器的那个双端口内存。

这个实现允许我们能够按照应用的需求改变PicoBlaze 的程序。你可以把这个方法当做是PicoBlaze 处理器的一种部分重配置功能。将新的程序下载到这个双端口RAM可以改变正在运行的系统PicoBlaze 处理器表现的功能,如果需要的话,执行不同的操作或者为了调试或者实验。我们也可以用这种方法在Zynq系统中更新多个 PicoBlaze处理器。

在下一篇博客中,我们将继续研究这技巧,我们将在Zynq芯片的PL侧控制和更新两个PicoBlaze 处理器 ,如下图所示:

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处