作者:Steve Leibson, 赛灵思战略营销与业务规划总监

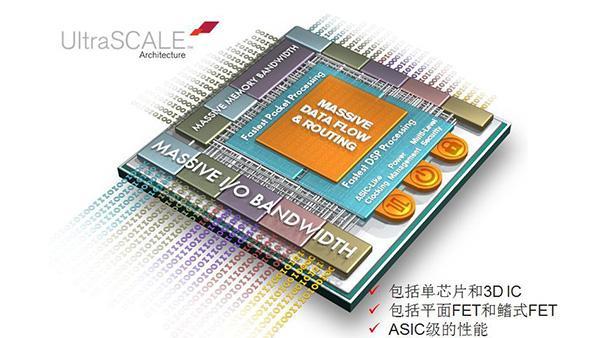

上周出版的最新一期的Xcell Journal杂志中刊载了由Nick Mehta主笔的一篇文章(“Productivity Skyrockets with Xilinx’s UltraScale Architecture”)(Xilinx UltraScale 架构能够快速提升生产力),下面是我们从Metha的文章中提取出了关于Virtex和Kintex UltraScale架构的FPGA和Vivado开发工具的一些主要的看点:

• 基于UltraScale架构的FPGA实现数据传输机制是通过将高性能的并行专用IO接口和高速的串行收发器结合起来实现的,UltraScale架构的串行收发器传送数据的速率能够达到16.3Gbps,满足主流的串行协议要求,当然传输速率也能够达到32.75Gbps,允许25G+比特位的地板设计,而且相对以前的收发器而言,能够大大降低每比特位传输的功耗。UltraScale架构的FPGA芯片中的收发器都兼容PCIe3.0和PCIe4.0,专用的PCIe集成模块支持PCIe3.0 X8型端口和根端口的设计需求。

• UltraScale架构包含了功能强大的可重配置时钟管理电路,主要包括时钟综合,缓存模块和布局组件,共同协作组成了高性能的时钟框架,能够满足各种设计的要求。这个时钟网络允许在FPGA内部灵活的对时钟信号进行布局布线,来降低时钟偏差、功耗和延迟,将时钟信号的传输误差降到最小。

• 与以往的FPGA相比,UltraScale架构的FPGA中的时钟分割和门控间隔技术能够提供对时钟功耗的额外控制。

• 如今的FPGA结构包含很多组件,例如可配置逻辑块(CLB),CLB中又包含六输入查找表(LUTS)和触发器;带有27x18乘法器的DSP;36Kbit的块RAM存储单元,支持内置FIFO和ECC。此外还有很多的逻辑功能,CLB支持移位寄存器,乘法器和进位逻辑,也能将LUT配置成分布式存储模块,当可配置的高效的块RAM资源不够时,这将是一个非常好的弥补方法。DSP组件也进行了更新强化,支持96比特位宽的XOR(异或)功能,支持27比特位的超前进位加法器和30比特位宽的输入信号,DSP部分能够独立完成很多功能,包括乘累加、乘加和模式识别等运算。

• UltraScale架构包含了几种流行的通信协议的集成模块。例如在Kintex和Virtex UltraScale系列的器件中集成了支持PCIe、100G以太网和150G Interlaken协议的多功能集成模块。

• 除了通信协议外,每个I/O模块包含了一个可编程存储器的PHY,通过MIG(存储器接口生成器)工具实现功能配置。

UltraScale架构和优化后的Vivado开发工具的推出,Xilinx为开发人员提供了高效率的解决方案,大大缩减了开发周期。

• Vivado IP封装器和IP核目录采用IP-XACT标准,这个标准时由SPIRIT Consortium创建的,已经成为封装、集成和重复使用IP核的标准结构,Vivado IP封装器可以将约束文件、测试激励文件和说明文档集成在一起,用于扩展你自己的IP核目录,可以保存问你自己的本地文件或者存放在一个共享的网络驱动器上。

• Vivado IP核目录允许开发人员将他们自己的IP核与Xilinx和第三方提供的IP核放在一起管理,这样采用一致的易于使用的方式,所有IP核可以再不同的设计团队之间共享使用。

• Vivado IP核集成器(IPI)采用以IP核为中心的设计流程,这样可以加快系统集成的时间,将系统的各部分组件更快更容易的集成在一起,形成一个系统。使用内部交互的图像化用户界面,IPI提供智能自动连接IP核接口,一键生成IP子系统和强大的调试功能,让设计开发人员能够以快速简单容易的方式将他们IP核目录里面的IP核连接集成在一起。

点击这里可以下载第89期Xcell Journal 杂志的PDF格式文档。

点击这里可以在线阅读第89期Xcell Journal 杂志。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/9-quick-bullets-on-the-Xili...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处