作者:Steve Leibson, 赛灵思战略营销与业务规划总监

任何在芯片间、板卡间或者暗箱间移动大量数据的系统设计都需要速度——很快的速度——在I/O带宽形式下:

•串行背板

•光接口

•主机和对等体通信

•芯片间通信

这是日前发布的赛灵思白皮书的主题,题目为“Leveraging UltraScale FPGA Transceivers for High-Speed Serial I/O Connectivity” (WP458),作者Brandon Jiao。这份24页的文件告诉你有关使用赛灵思20纳米UltraScale FPGA高速数字通信的所有要点。

例如:这是一张简易的图,展示了你能从每个Virtex UltraScale 和Kintex UltraScale系列成员中得到多少种类的SerDes收发器。

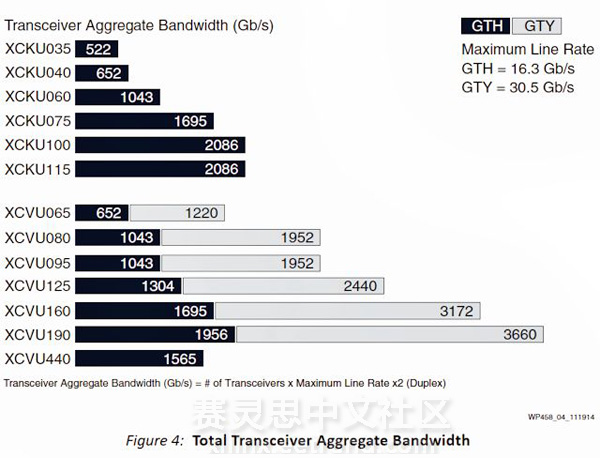

这是一张类似的图片,展示了从每个器件上的GTH和GTY收发器你能得到合计I/O带宽。

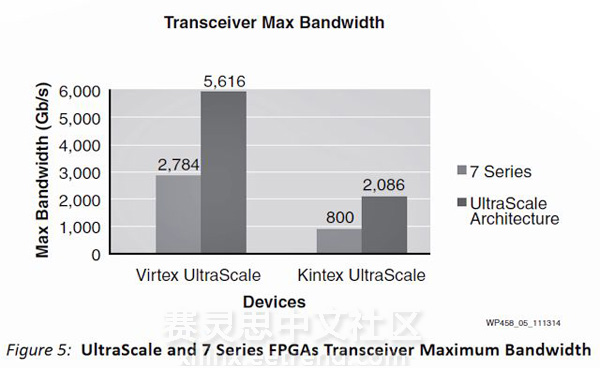

最后一张图比较了7系列和UltraScale Virtex和Kintex FPGA的合计器件带宽。

你的设计需要5.6Tbps,还是只要 2Tbps?

如果你想要深入了解更多关于使用这些UltraScale SerDes收发器的信息,你可以下载和阅读这篇新的白皮书。

© Copyright 2014 Xilinx Inc

如需转载,请注明出处